Testing as an Integral Part of a Product Life Cycle

By

**Terrence Chan**

# A MASTER OF ENGINEERING REPORT

Submitted to the College of Engineering at Texas Tech University in Partial Fulfillment of The Requirements for the Degree of

# **MASTER OF ENGINEERING**

Approved

Dr. A. Ertas

Dr. T.T. Maxwell

Dr. E.W. Kiesling

Dr. M.M. Tanik

October 16, 2004

### ACKNOWLEDGEMENTS

It has been quite an experience in the past fourteen months. I would like to thank my family, especially my wife. Our son Jeremy was only five-month old when I started this program. I definitely would not made it without her support and understanding. To Jeremy, I am sorry that I had to turn you away many times when you came to the study room wanted to play with me. I will try to make it up for you.

I would like to thank Dr. Ertas, Dr. Maxwell, Dr. Tanik and all of the professors and instructors for their teaching and sharing of their insights and wisdom. Special thanks to Dr. Ertas for developing such a unique program.

Last but certainly not least, I would like to thank my classmates Schuyler Deitch and John Zanoff. They provided so much motivation and encouragement to me throughout the entire program. Working with them together made our group assignments seemed so much enjoyable. I simply could not have asked for any better teammates than both of you. Thanks.

| ACKNOWLEDGEMENTS                                                                                                                                                                                    | II                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| DISCLAIMER                                                                                                                                                                                          | VI                   |

| ABSTRACT                                                                                                                                                                                            |                      |

| LIST OF FIGURES                                                                                                                                                                                     | VIII                 |

| LIST OF TABLES                                                                                                                                                                                      | X                    |

| CHAPTER I<br>INTRODUCTION                                                                                                                                                                           | 1                    |

| CHAPTER II<br>BACKGROUND                                                                                                                                                                            |                      |

| <ul><li>2.1 The Traditional Process</li><li>2.1.1 Waterfall Life-Cycle Model</li><li>2.1.2 Issues with the Waterfall Approach</li></ul>                                                             |                      |

| CHAPTER III<br>RAYTHEON LIFE CYCLE MODELS                                                                                                                                                           | 6                    |

| <ul> <li>3.1 Raytheon Life-Cycle Models</li> <li>3.2 Raytheon Waterfall Life-Cycle Model</li> <li>3.3 Incremental Life-Cycle Model</li></ul>                                                        | 7                    |

| <ul><li>3.5 Spiral Life-Cycle Model</li><li>3.6 Selecting Life-Cycle Model</li></ul>                                                                                                                |                      |

| CHAPTER IV<br>TESTING AS AN INTEGRAL PROCESS                                                                                                                                                        |                      |

| <ul> <li>4.1 Testing As An Integral Process</li> <li>4.2 Testing in Design Phase</li> <li>4.3 Testing in Development Phase</li> </ul>                                                               |                      |

| <ul><li>4.3.1 Prototyping</li><li>4.4 Testing in Integration Phase</li><li>4.5 Testing in Validation Phase and Production Phase</li><li>4.6 Dealing with Knowledge Loss</li></ul>                   | 17<br>17<br>18<br>18 |

| 4.6.1 Collaboration Tool<br>CHAPTER V                                                                                                                                                               |                      |

| LEVERAGING CURRENT TECHNOLOGIES                                                                                                                                                                     |                      |

| <ul> <li>5.1 Technologies that help</li> <li>5.2 JTAG (IEEE-1149.1)</li> <li>5.2.1 Some History</li> <li>5.2.2 Application</li></ul>                                                                |                      |

| <ul> <li>5.3 In-Circuit Test Flying Probe vs. Bed-of-Nails</li> <li>5.3.1 Bed-of Nails In-Circuit Test</li> <li>5.3.2 Flying Probe In-Circuit Test</li> <li>5.3.3 The Best of both worlds</li></ul> |                      |

| 5.4 Built-In-Test/Built-In-Test Equipment (BIT/BITE)                             | 32 |

|----------------------------------------------------------------------------------|----|

| 5.4.1 Commercial Application – Example : OBD-II                                  |    |

| 5.4.2 Military Application – A case study: Bradley A3                            |    |

| CHAPTER VI                                                                       |    |

| DESIGN FOR TESTABILITY                                                           |    |

| 6.1 Design For Testability (DFT)                                                 | 36 |

| 6.2 DFT Process                                                                  |    |

| CHAPTER VII<br>RAYTHEON INTEGRATED PRODUCT DEVELOPMENT SYSTEM (IPDS)             | 41 |

| 7.1 Introduction                                                                 | 41 |

| 7.2 Integrated Product Development Process                                       |    |

| 7.2 Test Engineering Process                                                     |    |

| 7.3 A Closer Look at IPDP                                                        |    |

| 7.4 The Importance of Test and Evaluation                                        |    |

| CHAPTER VIII                                                                     |    |

| SUMMARY AND CONCLUSIONS                                                          | 55 |

| REFERENCES                                                                       | 57 |

| APPENDIX A                                                                       |    |

| RAYTHEON INTEGRATED PRODUCT DEVELOPMENT SYSTEM                                   |    |

| Raytheon brings order to the confusion and chaos of high performance system desi |    |

| integration.                                                                     | -  |

| The Way We Do Business                                                           |    |

| Benefits of IPDS                                                                 | 1  |

| Get Raytheon's IPDS Working for You                                              | 2  |

| APPENDIX B                                                                       | 1  |

| A STUDY OF COMMERCIAL INDUSTRY BEST PRACTICES IN TEST AND                        |    |

| EVALUATION WHICH ARE POTENTIALLY APPLICABLE TO DOD                               |    |

| DEVELOPMENTAL TEST AND EVALUATION                                                | 1  |

| Overview                                                                         | 1  |

| Study Approach                                                                   |    |

| Selection of Companies                                                           |    |

| Efficiency and Effectiveness                                                     | 2  |

| Success Engenders Best Practices and Vice Versa.                                 |    |

| Conclusions                                                                      |    |

| APPENDIX C                                                                       |    |

| TEN TENETS OF INTEGRATED PRODUCT AND PROCESS DEVELOPMENT                         |    |

| DoDD 5000.1                                                                      |    |

| DoD 5000.2-R                                                                     |    |

| IPPD PROCESS                                                                     |    |

| 1. Customer Focus                                                                |    |

| 2. Concurrent Development of Product and Processes                               |    |

| <ol> <li>Early and Continuous Lifecycle Planning</li></ol>                       |    |

| T. Maximize regionary for Optimization and Use of Contractor Approaches          |    |

| 3 |

|---|

| 3 |

| 3 |

| 4 |

| 4 |

| 5 |

| • |

# DISCLAIMER

The opinions expressed in this report are strictly those of the author and are not necessarily those of Raytheon, Texas Tech University, nor any U.S. Government agency. An attempt has been made to acknowledge all the people involved in the material, but someone may have been missed. This is purely unintentional and it is my wish to acknowledge all sources for their material included in the report

## ABSTRACT

Having quality products that meet and exceed customer's requirement and expectation and in the same time remaining profitable are the keys to success. However, what does it take to manufacture quality product? Most companies emphasize in quality will have some kind for product development process. A process, if executed accordingly, can guarantee only repeatability, not necessary quality. Integrating testing into the product development is a significant factor contributing to quality.

It is common knowledge that it is much more cost effective to fix problems or design defects early in development. In practice, however, this is often neglected. Due to budget and time constraint, testing is frequently done in the last phase of development, the phase just before production. Test engineering is often not part of the design process. As a result, testing becomes a very costly and difficult task. Test engineers not only have to understand the details and characteristics of the design, they are confined to the testability limitation of the existing design. Because the design is already "set in stone", high test and fault coverage may not be attainable, or can be done cost effectively. Testing should be integrated to the product life cycle as a dynamic process.

The materials covered in this report are more applicable to products of the defense industry, specifically for deliverables that involve electronics and hardware.

# LIST OF FIGURES

| Figure 1 Traditional Product Development Cycle                                  | 4  |

|---------------------------------------------------------------------------------|----|

| Figure 2. Raytheon Waterfall Life-Cycle Model                                   | 6  |

| Figure 3. Incremental Life-Cycle Model                                          | 8  |

| Figure 4. Evolutionary Life-Cycle Model                                         | 10 |

| Figure 5. Spiral Life-Cycle Model                                               | 11 |

| Figure 6. Another View of Spiral Life-Cycle Model                               | 11 |

| Figure 7. Testing as an Integral Part of Development Cycle                      | 14 |

| Figure 8. Documentum eRoom User Interface                                       | 20 |

| Figure 9. eRoom Project Plan with Auto Notification of events and Delinquencies | 21 |

| Figure 10. I/O Ports with loopback capability                                   | 25 |

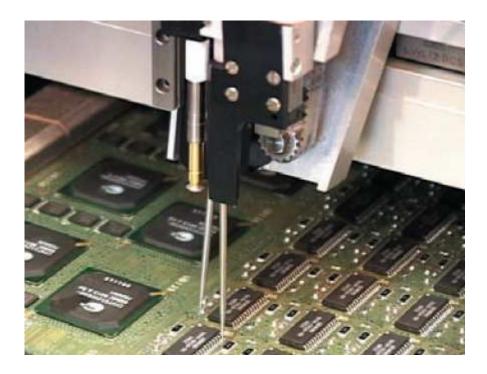

| Figure 11. ICT Bed-of-Nails fixture                                             | 28 |

| Figure 12. Flying Probe Testing a Printed Circuit Card                          | 30 |

| Figure 13. Agilent 3070 In-Circuit Test                                         | 31 |

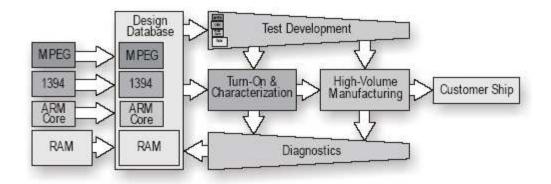

| Figure 14. SOC Development Process                                              | 37 |

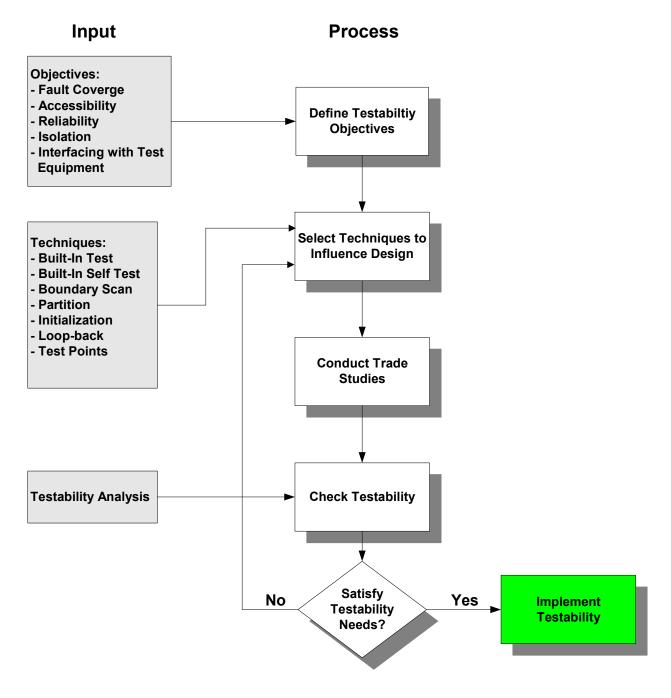

| Figure 15. Process for Design for Testability                                   | 39 |

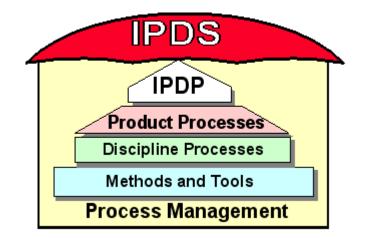

| Figure 16. Structure of Integrated Product Development System                   | 41 |

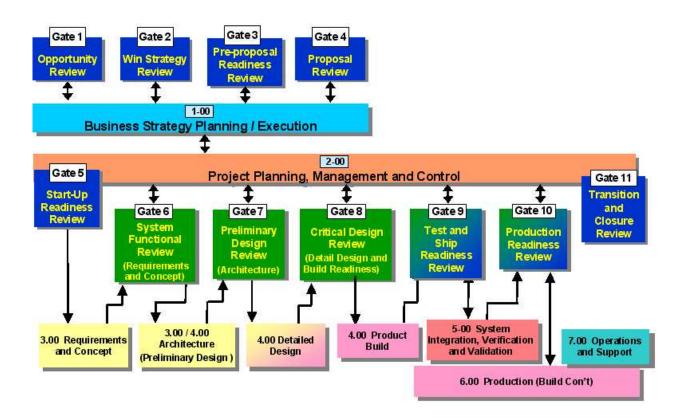

| Figure 17. IPDP Architecture                                                    | 44 |

| Figure 18. IPDP Gates                                                           | 45 |

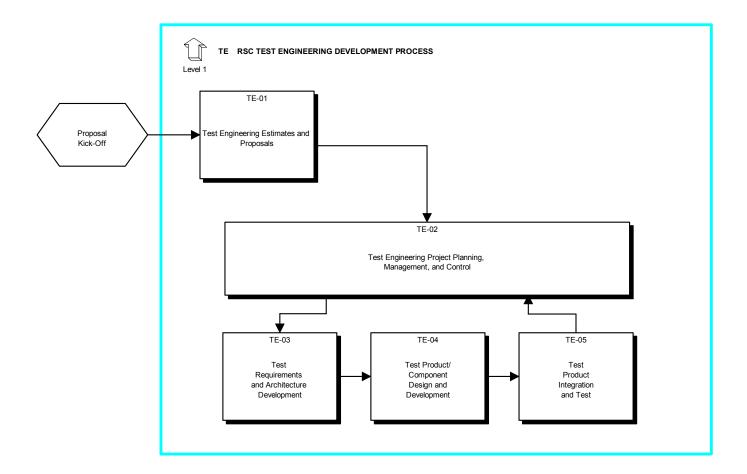

| Figure 19. Test Engineering Development Process Top Level Flowchart             | 46 |

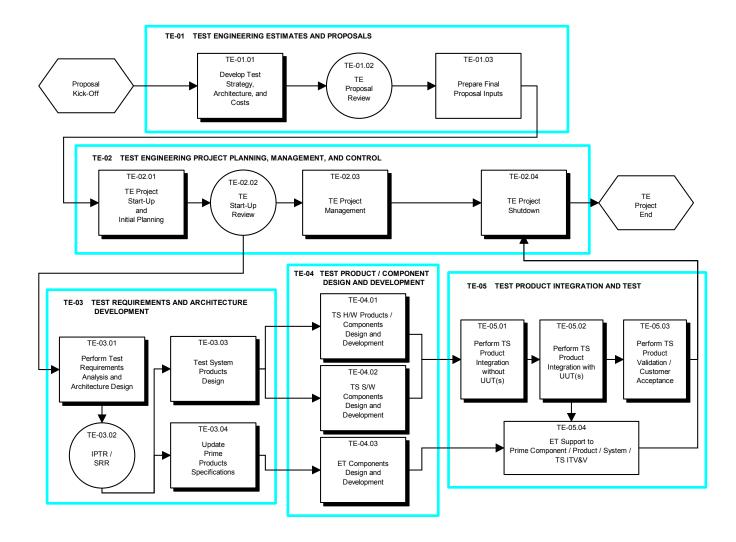

| Figure 20. A Detailed View of TEDP                                              | 47 |

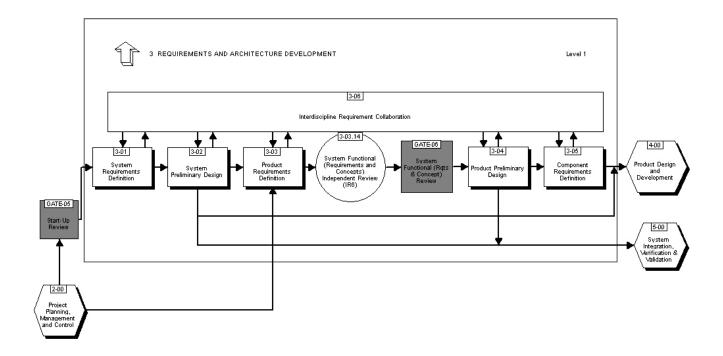

| Figure 21. Stage 3 Requirement and Architecture Development                     | 49 |

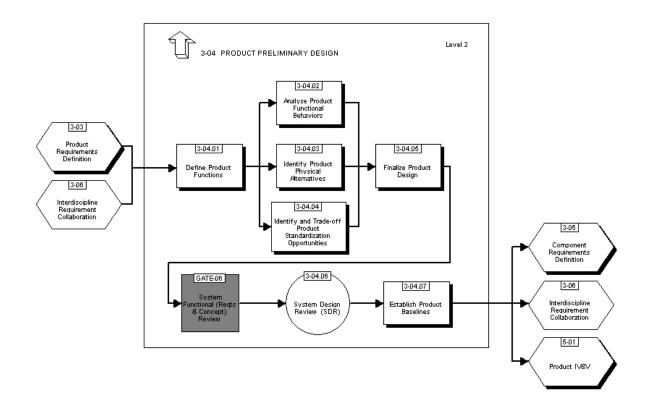

| Figure 22. Product Preliminary Design Flow Chart                                | 49 |

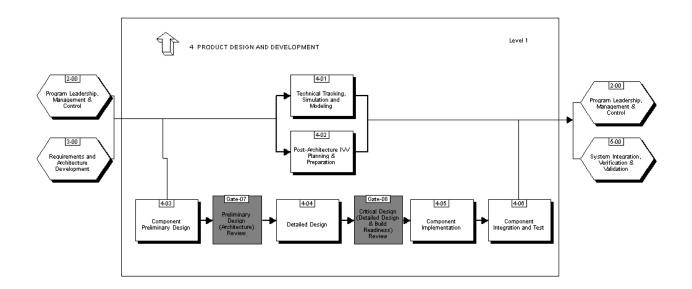

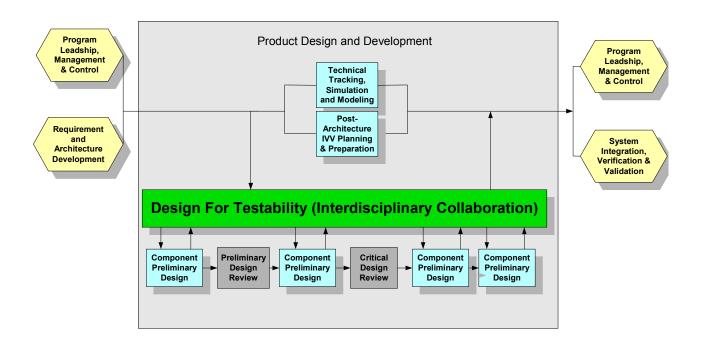

| Figure 23. Product Design and Development                                       | 50 |

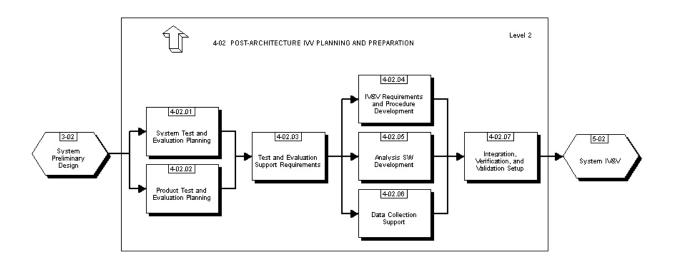

| Figure 24. Post-Architecture IVV Planning and Development                       | 51 |

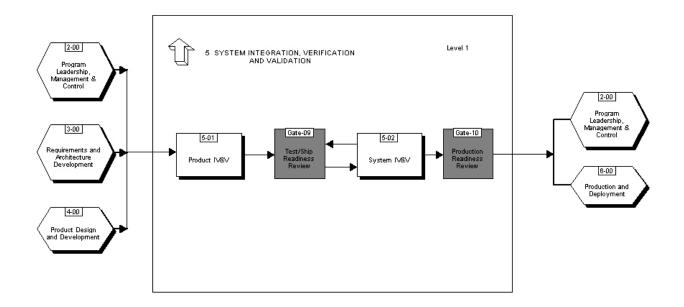

| Figure 25. System Integration, Verification and Validation                     | 51 |

|--------------------------------------------------------------------------------|----|

| Figure 26. Product Design and Development with Interdisciplinary Collaboration | 52 |

# LIST OF TABLES

| Table 1 LCM Selection Criteria Matrix | 13 |

|---------------------------------------|----|

| Table 2 IEEE 1149.1 TAP Signals       | 23 |

# CHAPTER I INTRODUCTION

In this highly competitive market, companies are under constant pressure to deliver quality products and to meet or exceed customer requirement within budget and schedule constraint. To fulfill this goal and to ensure consistent product quality, most companies would employ some form of product development and production process. The traditional process typically follows these phases in sequence: Design Phase, Development Phase, Integration Phase, Validation Phase and Production/Manufacturing Phase. During the process, some testings are done in different phases to check whether the design or product meets the requirement. However, these testing efforts very often are not in an organized manner. While this process defines a road map for the entire development life cycle, its result does not guarantee a quality product.

Companies that consistently delivery quality products tend to have a common perspective: they recognize the important of testing to identify and solve problems early in the process in order to control time, cost and schedule late in the process [13: Science Applications International Corporation, 2002]. The quality of a product does not solely depend on how well quality control is executed during the production and manufacture process. If design detects are not identified and solved, the end product is only going to be as good, or bad in this case, as the design. To ensure the quality of a product, it needs to begin very early in the design phase and flows down to the entire process.

This report will look at the most commonly use product Life Cycle Models (LCM) namely Waterfall, Incremental, Evolutionary and Spiral. It will then look at how to integrate test and evaluation throughout the entire product life cycle process. This process can identify levels of performance and assist the developer in correcting deficiencies. It is also a significant element in the decision-making process, providing data supportive of trade-off analysis, risk reduction and requirement refinement. As technology advances, testing techniques and standard are constantly being updated. This report describes some techniques and technologies that can improve the development process and are readily available today. Utilizing these techniques and technologies can greatly increase testability and reduce risks and cost. They should be employed as "best practices" to improve the development process. Design for Testability is another important tool that can greatly improve the cost and development of testing. Finally, this report will discuss briefly on Raytheon's Integrated Product Development Process (IPDS). Suggestions will be made to improve the process.

The objective of this study is to investigate the important of test and evaluation as an integral part of the product life cycle.

# CHAPTER II BACKGROUND

#### **2.1 The Traditional Process**

#### 2.1.1 Waterfall Life-Cycle Model

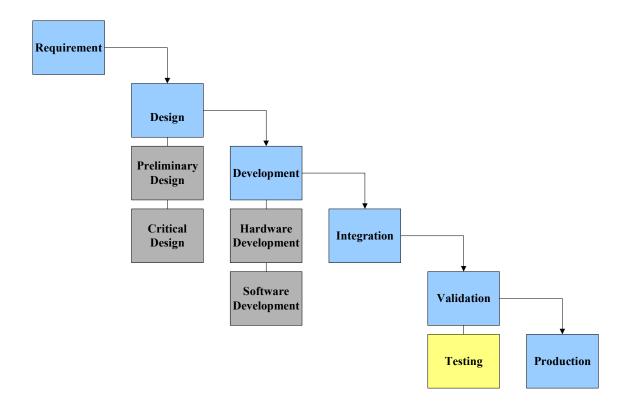

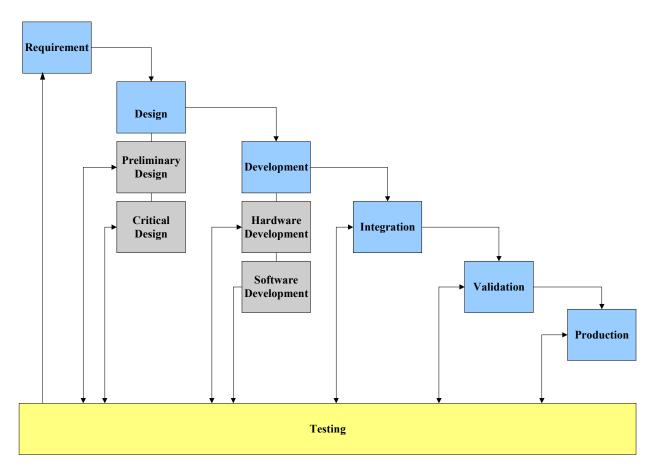

Traditional product life cycle (design, development and production) is of a waterfall model (see Fig. 1). It starts with a Requirement Phase to define the customer and/or product requirement. Then it follows by a Design Phase to define the design approach that will meet the defined requirement. Trade studies will be done at the phase to determine the effectiveness and cost of different design approaches. Once the design is solidified, it will move on to the Development Phase. In this phase, the actual design will be implemented usually in some form of prototyping. The development will include hardware and any necessary software. Once the prototype is proven viable, it will proceed to the Integration Phase. In this phase all the details of the design are finalized here. Hardware is built, and software is developed. Both hardware and software are integrated together as development progresses. As the Integration Phase is complete, the Validation Phase to produce and manufacture the actual product. The Production Phase often begins at the Integration Phase to prepare any tooling and necessary supports needed for the production.

The advantage of this waterfall model is that it provides a systematic approach. Each phase of the process is well defined. Milestones can be set for each phase to determine progress. The model also fits well with the general systems engineering process, such as the Integrated Master Plan (IMP) and Integrated Master Schedule (IMS).

Figure 1 Traditional Product Development Cycle

## 2.1.2 Issues with the Waterfall Approach

While the waterfall approach is useful to define a road map for the entire development process, it also has many shortcomings. The quality of a product is not only a matter of how well quality control during the production and manufacture process. The quality control of a product begins at the Design Phase and flows down to the entire process. A perfect production and manufacture process does not guarantee a quality product; it only guarantees the product will be made to the specified design with the defined tolerance. Any design detects are flowed down directly to production.

Some levels of testing are performed during the design phase and development phase. However, these testing efforts very often are done in an ad-hoc manner, and the knowledge gained is not documented and captured. Most of the formal testing effort, unfortunately, is spent during the later period

of the system integration and validation. Test engineers who have little or no involvement with the design and development now have the task to fully test the product. To verify whether a design is fully compliant to the requirement requires in depth understanding of both the requirement and the design. It is a very demanding task and inherently has a steep learning curve. In the fast pace of most work environment, the designers of the product will move on to other projects after the design phase is completed. The knowledge that was gained during the design phase is not effectively passed on to the next phase. Testing tools developed during design and development phases to verify the functionality of the design were frequently not documented. As the result, test engineers very often have to "re-invent the wheel". Knowledge lost is a serious problem in the waterfall model.

Cost for testing during the later period of the system integration and validation is also very high. Test engineers have to acquire acknowledge and understanding of the design. This effort is very time consuming and costly. The original product designers may not be available during this time to answer questions or to explain the reasons why certain design approaches are chosen. Product designers whom do not have testing experience may overlook the feasibility of testability completely and render testing very difficult and costly if not impossible. Other times product designers may have planned for testability but are forced to forego the effort because of budget and schedule constraint.

# CHAPTER III RAYTHEON LIFE CYCLE MODELS

# 3.1 Raytheon Life-Cycle Models

Raytheon Integrated Process Development System (IPDS) identifies four most common Life Cycle Models (LCM), namely Waterfall, Spiral, Incremental and Evolutionary. The details of each LCM are given in the following sections [4: Raytheon IPDS, 2003].

## 3.2 Raytheon Waterfall Life-Cycle Model

The Raytheon Waterfall LCM is very similar to the traditional Waterfall LCM in Section 2.1.1. Due to the similarity, the Raytheon LCM will not discussed in details. Figure 2 depicts the Raytheon Waterfall LCM.

Figure 2. Raytheon Waterfall Life-Cycle Model

## 3.3 Incremental Life-Cycle Model

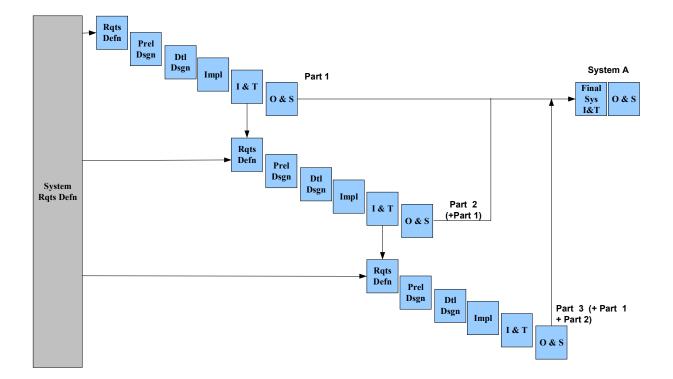

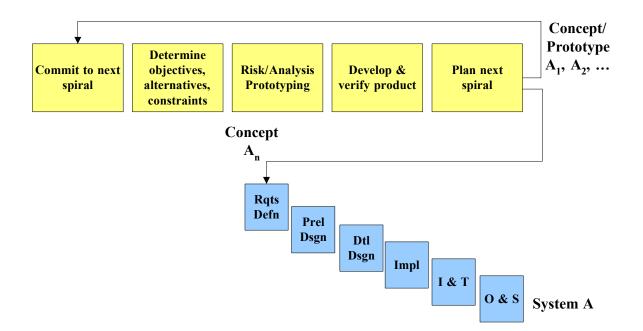

In Incremental Life-Cycle Model, products are designed, implemented, integrated and tested in a series of additive builds (see Figure. 3). Each increment has a series of phases identical to the Waterfall Life Cycle Model: Requirement Definition (Rqts Defn), Preliminary Design (Prel Dsgn), Detail Design (Dtl Dsgn), Implementation (Impl), Integration and Test (I & T) and Operations and Support (O & S). Each build completion provides demonstrable functionality or capability, adding to the final system completion (assembling a puzzle). It allows the customer to evaluate the incremental system products and make recommendations for change (early in development). It facilitates risk mitigation (can work risky areas early or defer them until later when more knowledge is gained). It enables step-wise validation of requirements (targeted around functions/capabilities. It tends to force a highly modular and upgradeable structure (reusable architecture that supports Life-Cycle improvements). System requirements need to be defined only once then update based on results during design.

One of the major advantages of Incremental LCM is that it provides early mitigation of high risk items. High risk items can be built first, with possible alternatives develop in parallel. The lower risk system elements are completed as appropriate for the selected alternative. This LCM is very useful when the customer does not know exactly what they want or need to fulfill the mission. The customer feedback is obtained at the end of each build, and changes and adaptations can be made accordingly. Lessons learned can be applied subsequent builds.

Figure 3. Incremental Life-Cycle Model

The Incremental LCM, however, has its weaknesses. It requires robust system architecture with high cohesion and low coupling. Such architecture is difficult to achieve and requires extremely detailed planning. It also requires strong systems engineering to define, establish and manage system level requirements and system models. Being incremental in nature, there is always a tendency to attempt to redefine or re-do all of the system requirements with each incremental build. During each build, there is also constant temptation to re-design elements/components that are already complete. A system framework should be established for the next incremental build to be added or refined based on the results of the current incremental. Incremental LCM also requires disciplined process planning and execution. The development can degenerate into a build-fix approach if the customer is allowed to make ad hoc requirement, design and implementation changes. Current build must be constrained by previous builds. Incremental LCM is prone to requirement/scope creep driven by too much customer feedback.

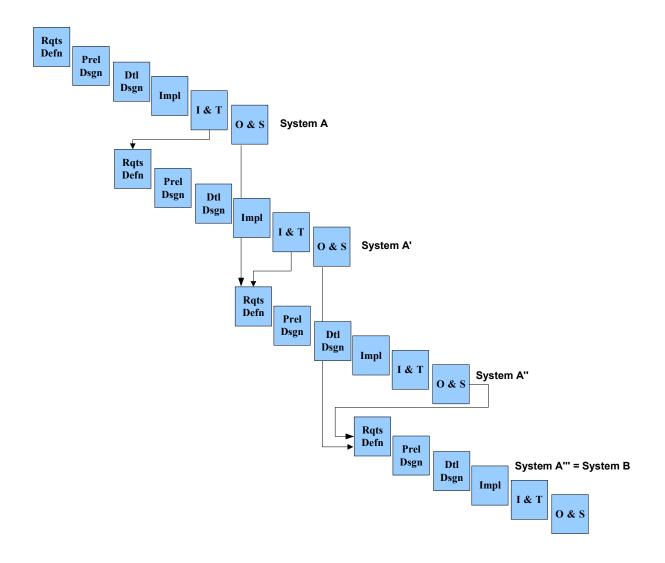

# 3.4 Evolutionary Life-Cycle Model

The Evolutionary Life-Cycle Model is a series of developmental efforts each of which typically or potentially leads to a deliverable product. Figure 4 depicts the Evolutionary LCM. Each effort represents a full development cycle, including requirements analysis. Operational feedback is obtained from an operational and fielded product and then applies to subsequent efforts. This may result in substantial requirement change. Evolutionary LCM can accommodate technology insertion that is not yet well-defined or existing at the moment.

#### **Figure 4. Evolutionary Life-Cycle Model**

Similar to Incremental LCM, Evolutionary LCM facilitates early risk mitigation. It is very flexible and can accommodate significantly changed requirements, requirements perhaps not known in the initial conception. Through the Integration and Test Phase in each build, the requirements are further refine and clarify. Evolutionary LCM also provides user with operational capability early in the project. Valuable end-user feedback is obtained from each delivery. Anther strength of the Evolutionary LCM is that it can adapt new technology insertion and evaluation over the project lifetime.

The Evolutionary LCM has, of course, its weaknesses. Schedule gap is likely to exist between the end of one effort and the start of the next effort, causing down time and staffing issues. Engineers may have to move on to other projects resulting potential loss of knowledge. The customer may accept a product, that deemed "good enough", prior to completing all planned efforts. This can have significant impact to long-term organizational plans. Architecture, design and implementation decisions may impact subsequent efforts. Temporary workarounds within a development phase can become unchangeable constraints. As the product life-cycle evolve, the system may bear little resemblance or share little reuse in common with the starting system.

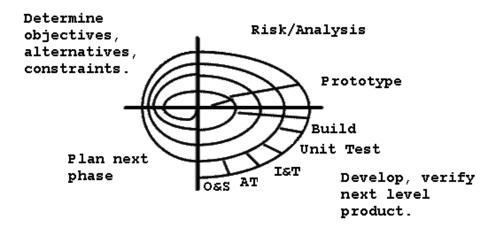

## 3.5 Spiral Life-Cycle Model

The Spiral Life-Cycle Model is a modified Waterfall LCM such that the spiral "front end" is the system definition and rapid concept development (see Figure 5 and Figure 6). The Spiral LCM is mostly used for internal company development. It can rapidly develop system concepts and encourage Integrated Product Team (IPT)/Multi-disciplinary participation. Through the spiral process, design issues and constraints can be quickly identified before the system concept is set-in-stone.

**Figure 5. Spiral Life-Cycle Model**

Figure 6. Another View of Spiral Life-Cycle Model

One of the major weaknesses of Spiral LCM is that it is difficult to clearly define the exit criteria in each iteration of the spiral. Engineers often have the tendency to get trapped in the "spiral" mind set, "it

will be better design if I can spend more time on it". This behavior may continue even after detail design efforts are already under way.

# 3.6 Selecting Life-Cycle Model

Each of the LCM has its own strengths and weakness. Raytheon IPDS provides guidelines for the LCM selection criteria (see Table. 1).

| Characteristic                                                         | Criteria                     | W | I   | Е   | S   |

|------------------------------------------------------------------------|------------------------------|---|-----|-----|-----|

| Time Relationship between Data & Processing                            | Static                       | • | •   | ٠   | ٠   |

|                                                                        | Dynamic                      |   | ٠   | ٠   |     |

| External Debayiar of Majority of Entition and Objects                  | Data Intensivo               |   |     |     |     |

| External Behavior of Majority of Entities and Objects<br>in the System | Data Intensive               |   | •   | •   | •   |

|                                                                        | Control Intensive            |   |     | •   | •   |

|                                                                        | Algorithmic Intensive        | • | •   |     | •   |

|                                                                        | 5                            |   |     |     |     |

| Predictability of Problem Solution                                     | Deterministic                | • | •   |     | ٠   |

|                                                                        | Non-deterministic            |   | •   | •   |     |

| System Complexity                                                      | Low                          | • | •   |     | •   |

|                                                                        | Medium                       | • | •   | •   | •   |

|                                                                        | High                         |   | •   | •   |     |

|                                                                        |                              |   |     |     |     |

| Development Duration                                                   | < 1 year                     | • | ٠   |     | ٠   |

|                                                                        | 1 - 3 years                  | • | ٠   |     | ٠   |

|                                                                        | > 3 years                    |   | •   | •   |     |

| Project Management / Project Control Cost Impacts                      | Additive factor compared to  |   |     |     |     |

|                                                                        | Waterfall                    | 0 | 0.2 | 0.3 | 0.2 |

|                                                                        |                              |   |     |     |     |

| Acquire a Staff in Time for Project Execution                          | All available                | • | •   | •   | •   |

|                                                                        | Some available               |   | •   | ٠   | ٠   |

| Changes to a Fielded / Heritage System                                 | Small to moderate changes to |   |     |     |     |

|                                                                        | heritage system              | • |     |     | •   |

|                                                                        | Large changes to heritage    |   |     |     |     |

|                                                                        | system                       |   | •   | •   |     |

| Frequency of Anticipated Changes                                       | Low                          | • | •   | •   | •   |

| (Requirement Volatility)                                               | Medium                       |   | •   | •   | •   |

|                                                                        | High                         |   |     | •   |     |

|                                                                        |                              |   |     |     |     |

| Anticipated Magnitude of Requirement<br>Changes (Scope/Depth of System)    | Low<br>Medium<br>High                                                                   | • | •      | •<br>• | • |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---|--------|--------|---|

| Technology Insertion                                                       | Existing technology<br>New technology<br>Future technology (within project<br>lifetime) | • | •      | •      | • |

| Anticipate Scope of Requirement Change (Breadth)                           | Small<br>Medium<br>Large                                                                | • | •<br>• | •<br>• | • |

| What is the Ability to Mitigate Risk As a<br>Life-Cycle Model?             | Low<br>Moderate<br>High                                                                 | • | •      | •      | • |

| Requirements Maturity (#TBDs or #TBRs),<br>1 - (#TBDs+ TBRs / #TOTAL Reqs) | Mature<br>Moderately Mature<br>Immature                                                 | • | •      | •<br>• | • |

Note: Lack of a "• "means that the LCM is not as well-suited; it can still be used, however.

## Table 1 LCM Selection Criteria Matrix

Based on these criteria, Incremental and Evolutionary LCM seem to be the better choices for projects with higher risk and higher anticipated requirement changes. In practice, however, projects and systems that involve deliverable items of integrated hardware and software rarely use the Incremental and Evolutionary LCM. This is partly due to the fact that the customer (in this case the Department of Defense) and engineers in the defense industry are not accustomed to these Life-Cycle Models. However, there is interest from DoD in considering the use of Incremental and Evolutionary. These projects typically are projects where rapid prototyping is more feasible (such as the ones that are more software oriented). The Waterfall LCM is still the most frequently use Life-Cycle Model.

# CHAPTER IV TESTING AS AN INTEGRAL PROCESS

# 4.1 Testing As An Integral Process

Testing should be an integrated and iterative process throughout the product life cycle (see Fig. 7). It identifies levels of performance and assists the developer in correcting deficiencies during each phase of the product life cycle. From systems engineering perspective, test planning, testing, and analysis of test results are integral parts of the basic product definition process. Systems engineering has been defined in the Department of Defense (DoD) context: Systems engineering is an interdisciplinary approach to evolve and verify an integrated and optimally balanced set of product and process designs that satisfy user needs and provide information for management decision making.

Figure 7. Testing as an Integral Part of Development Cycle

Testing is a significant element in the decision-making process, providing data supportive of trade-off analysis, risk reduction and requirements refinement. Testing actually consists of two distinct aspects: Test and Evaluation. Test denotes the actual testing of subject under test – hardware, software, models, prototypes, production equipments, design concepts – to obtain data, both quantitative and qualitative. Evaluation denotes the process whereby data are logically assembled, analyzed and compared to expected performance to aid in making systematic decisions.

One of the main purposes of testing is to identify the areas of risk to be reduced or eliminated. Testing has many useful functions and provides information to people with different needs. It gives information to developers for identifying and resolving technical difficulties; to decision makers responsible for managing the project and for the best use of limited resources; and to the customers/end-users for refining requirements and supporting development of effective procedures. Test and evaluation is also an iterative process. As issues and problems are identified during each phase, corrective actions are taken to resolve the problems so that they will not propagate unnoticed to the next phase.

# 4.2 Testing in Design Phase

The primary objective of testing in the design phase is to influence system design. Design evaluation should be fully integrated into the development test cycle; and its purposes are to:

- Determine if critical system technical characteristics are achievable

- Provide data for refining and making the hardware more rugged to comply with technical specification requirements

- Eliminate as many technical and design risks as possible or to determine the extent to which they are manageable

- Provide for evolution of design and verification of the adequacy of design changes

- Provide information in support of development efforts

- Ensure components, subsystems and systems are adequately developed before beginning operational tests

- Develop test cases and tools to verify the design. Keep in mind that these tools will be integrated together as a test system at the end.

# 4.3 Testing in Development Phase

Integrating test and evaluation in the development phase is especially important in complex systems. Complex systems have to be divided into smaller sub-systems in order to be manageable. The interfaces of the sub-systems must be well defined in order to guarantee the system will function properly when all the sub-systems are integrated together. Sub-system level testing can verify all the necessary interfaces and the sub-system itself meeting the specification. In reality, this can be a very difficult task. It is crucial to identify design issues as early as possible. Defects and design issues cost much less to fix at design phase and development phase. This is especially true for complex systems. Ideally, failure on one component should only affect the immediate sub-assembly. By isolating and fixing the failure of that particular component, the other sub-assemblies and higher assemblies should not be affected. However, in the case of systems that are more inter-dependent, failure in a single sub-assembly could affect the entire system. For example, optical systems that require precise optical alignment and tight tolerance may fall into this category. Fixing a sub-assembly in an optical system may require re-alignment for all assemblies of the entire optical path. The re-alignment can be labor intensive and very costly. Product designers should eliminate as much single-point failures as possible.

As electronics design becomes more and more complex and constant advancing of technology, hardware designers are facing difficult challenge to come up with robust designs. Design for Testability is one of the most cost-effective ways of tackling quality problems. It is only effective, however, if it is performed properly and at the proper time. It is also important to utilize previously used and develop new test cases, tools and test equipment to verify the design.

# 4.3.1 Prototyping

Rapid prototyping is the desire method to ensure the design would meet the defined requirement. A design that meets all requirement and works perfectly the first time only happens in the realm of fiction. Prototyping allows problems to be identified early design and development. Prototyping is most beneficial for software product or product that has a large amount of user-interface. It is extremely valuable if the customer can involve in this process. Direct feedback can be obtained from the customer to be sure it will meet the customer needs and expectation.

However, for product that are hardware oriented, rapid prototyping may not be feasible. Testing is even more important if very limited prototyping is allowed. All the critical parameters of the product need to be tested. Due to the complexity of today's electronics and very often the design tasks are spread to multiple teams, design issues or faults are likely found in preliminary design. There are many techniques that are available to ease the task of testing. They will be discussed in details in the following chapter.

# 4.4 Testing in Integration Phase

This is the phase of the development where the system gets integrated together. Testing is done to ensure components, subsystems and systems are integrated properly. All the interfacing issues should be tested and worked out here. The final goal is to verify the functionalities of the integrated system meet the requirements. Again, the test tools and equipments that have been built up are utilized to verify the system functionalities. A test set maybe develop here for automating functional tests if a functional test set is required or if such a test set is valuable for production testing. Base on functional test results, minor changes and modifications are made to the design. Reworks and redesign are costly at this point. Hopefully, major changes and issues are addressed prior to this phases.

# 4.5 Testing in Validation Phase and Production Phase

Testing in validation phase is the final testing of the product to verify whether it meets all of the requirements. A functional test set if required or needed should be complete in this phase and to serve as the test bed for validating the system.

After the system has been validated, the process will move on to the production phase. The functional test set developed during the development can be used in the production phase to verify each production system meets all the requirements. Test data collected during production testing can aid and identify detects that points to faulty components or manufacturing processes. It can also identify possible and potential design defects and weaknesses that need to be addressed in the future revisions.

## 4.6 Dealing with Knowledge Loss

As mentioned earlier, knowledge lost is a serious problem in the waterfall model. Different test activities take place during the design phase and development phase. Very often, hardware and product designers may even develop tools and hidden features to aid testing and verifying the design. These tools maybe experimental in nature but yet provide some fundamental and crucial testing. For example, I often found hardware engineers create additional functions in the FPGA code. These functions are not part of the device requirement but yet they are very useful tools to verify the functionality of the FPGA and the other components that are linked to the FPGA as well. However, these functions in most cases are not documented. As the hardware and product designers move on to other projects, the knowledge is also lost.

To be value-added to the product life cycle, test activities must be a coordinated effort. Collaboration between design, software, hardware and test engineers not only can improve the design of a product; it can have extensive cost saving as well. In the previous example of hidden features developed by hardware and product engineers, these hidden features can possibly to great tools during the acceptance test of the product. With the help of test engineers, many of these test activities can be developed as tools that can be re-used through the different phases of the product development cycle.

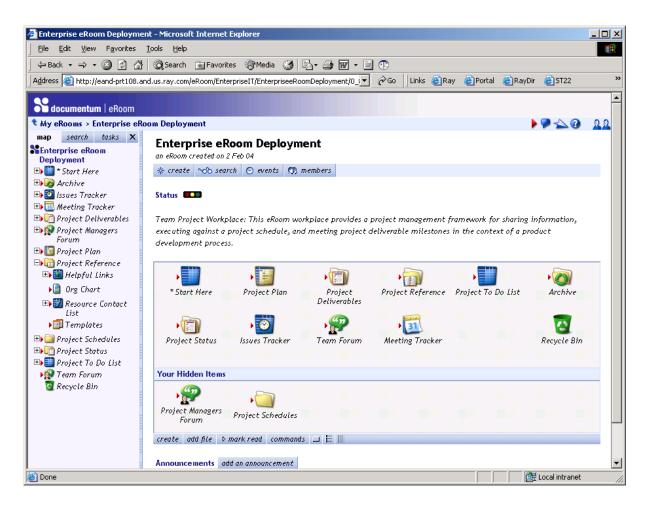

#### 4.6.1 Collaboration Tool

Starting April 1, 2004, Raytheon is implementing Documentum eRoom as the enterprise standard Teamware service. eRoom, a collaboration tool, provides a virtual space or 'room' for members of a project team to plan, collaborate, make decisions and accomplish their team objectives. eRoom is web-based tool supporting team collaboration through document sharing, electronic discussions and decision making, shared databases and team calendaring. Figure 8 shows the user interface of eRoom [11: Raytheon RTN Collaboration Center, 2003].

eRoom has the Project Plan (see Figure 9) function that can keep track of the project progress, set up milestone and notify users if certain tasks are overdue [11: Raytheon RTN Collaboration Center, 2003]. eRoom also provides access control. Depending on the role of the user, the user may create, edit, view different entries within eRoom. A project team can create a 'room' that contains as many user-defined databases as needed for such purposes as milestones, issues, contacts, action items, document approvals, etc. A forum can be set up within eRoom for users to discuss issues they encounter during the development of the project. eRoom is web-based application that users and can access 24/7 across the globe. Useful information such as lessons learned can be captured in a database anytime during the development, not afterward while some of the knowledge can possibly be lost or incorrect. This is extremely helpful in solving the issue with knowledge loss during the product life cycle.

Figure 8. Documentum eRoom User Interface

# Project Plan 💊 edit

a project plan created by 🖂 eRoom on 22 Jan 03

|  | new task | all tasks | ungrouped 💌 in weeks | ▼ | start chart on 8/1/2003 | 🔟 go today |  |

|--|----------|-----------|----------------------|---|-------------------------|------------|--|

|--|----------|-----------|----------------------|---|-------------------------|------------|--|

Use the Project Plan to track the status and progress of projects and tasks.

#### The Start Date for the Sample Project is August 1, 2003. Use this date to navigate through the Gantt chart view of the Project Plan.

| 📃 task rema | ining 🔳 task done 📰 not counted            | РО п | ilestor | one 📃 overall duration                 |

|-------------|--------------------------------------------|------|---------|----------------------------------------|

|             | Task                                       | ID   | Dur.    | ⊔ Gantt                                |

|             |                                            |      |         | 3 Aug 03 10 Aug 03 17 Aug 03 24 Aug 03 |

|             | All tasks 18                               |      | 55d     |                                        |

|             | Review internal product reqs.<br>database  | 2    | 1d      |                                        |

|             | Define target market<br>characteristics    | 1    | 5d      |                                        |

| 🗖 🖬 💊 🕨     | Create product reqs. document              | 3    | 3d      |                                        |

|             | Market feedback - internal focus<br>groups | 4    | 2d      |                                        |

|             | Market feedback - industry<br>analysts     | 6    | 2d      |                                        |

| 🗖 🖬 🕥 🕨     | Market feedback - external focus           | 5    | 4d      |                                        |

Figure 9. eRoom Project Plan with Auto Notification of events and Delinquencies

# CHAPTER V LEVERAGING CURRENT TECHNOLOGIES

#### 5.1 Technologies that help

Many technologies are available to help ease the task of test and evaluation. One common characteristic of these technologies and tools is that they need to be carefully planned early in the development cycle because they have great impact to the design and architecture.

## 5.2 JTAG (IEEE-1149.1)

## 5.2.1 Some History

The traditional method of testing circuit card was bed-of-nails which employed small spring loaded test probes to make connections with solder pads on the bottom of the board. The test fixtures were custom made and expensive, and much of the testing could not be performed until the design is complete. As circuit boards get smaller and surface-mount packaging technology improved, the bed-ofnails method becomes ineffective and inefficient.

A group of European electronics companies formed a consortium in 1985 called the Joint Test Action Group (JTAG) to address the problems with circuit card testing [8: JTAG Technologies, 2001]. The result was a specification for performing boundary-scan hardware testing at the integrated circuit (IC) level. In 1990, the specification was standardized to become IEEE 1149.1, a standard that established the details of access to any chip with a JTAG port. IEEE 1149.1 is a standard specifying how to control and monitor the pins of compliant devices on a printed circuit board. The specification IEEE 1149.1 devised uses boundary-scan technology, which enables engineers to perform extensive debugging and diagnostics on a system through a small number of dedicated test pins. Signals are scanned into and out of the I/O cells of a device serially to control its inputs and test the outputs under various conditions.

| Signal Name | Required | Description             |

|-------------|----------|-------------------------|

| TDI         | Yes      | Test Data Input         |

| TDO         | Yes      | Test Data Outpug        |

| тск         | Yes      | Test Clock              |

| TMS         | Yes      | Test Mode Select        |

| TRSTB       | Optional | Test Reset (Active Low) |

#### Table 2 IEEE 1149.1 TAP Signals

The IEEE 1149.1 standard only outlined the addition of a set of four (optionally five) Test Access Port (TAP) pins to the device package and the op-codes for the 16 state machine that allows the observation and control of the device states. Table 2.0 depicts the TAP signals on the JTAG interface [10: Leroy's Engineering, 1998]. The definition and adoption of IEEE 1149.1, as the circuit board testing community called it, was the most promising advances in electrical testability in the decade of the 90s. However, only in recent years have Automated Test Equipment (ATE) manufacturers begun to embrace the standard in software that is able to quickly generate test coverage for both single components and chains of IEEE 1149.1 compliant devices. Interconnection Boundary Scan components into chains by tying the output of one component to the input of the next is the real key to decreasing the test access requirements of predominantly digital assemblies. There is even more sophisticated software that enables the generation of automatic tests of components that are non-scan compliant, using the boundary scan register instead of tester electronics. This technique further decreases the test access requirements of the circuit board.

## 5.2.2 Application

Most devices such as Digital Signal Processors (DSP), Field Programmable Gate Arrays (FPGA), Application Specific Integrated Circuits (ASIC) have JTAG built-in or can have JTAG implemented. These devices can be seen at many commercial and military electronics. The standard test process for verifying a device or circuit board using boundary-scan technology is as follows:

- The tester applies test or diagnostic data on the input pins of the device.

- The boundary-scan cells capture the data in the boundary scan registers monitoring the input pins.

- · Data is scanned out of the device via the TDO pin, for verification.

- Data can then be scanned into the device via the TDI pin.

- The tester can then verify data on the output pins of the device.

Simple tests can find manufacturing defects such as unconnected pins, a missing device, an incorrect or rotated device on a circuit board, and even a failed or dead device. The primary advantage of boundary-scan technology is the ability to observe data at the device inputs and control the data at the outputs independently of the application logic.

Another benefit is the ability to reduce the number of overall test points required for device access. In traditional circuit card design, test signals are brought out to the primary connector or to its dedicated test connector. For more complex circuit cards that require many analog and digital signals, the primary connector may barely have enough pins to accommodate these signals. Reserving pins for test signals sometimes are not feasible. A separate test connector for the test signals maybe viable in some cases, but it increases the cost in fabrication. Other times the test connector may not be accessible at a higher assembly level, limiting testing only available at lower assembly level. With boundary scan, there are no physical test points. This can help lower board fabrication costs and increase package density.

Boundary scan provides a better set of diagnostics than some other test techniques. Conventional techniques apply test vectors (patterns) to the inputs of the device and monitor the outputs. If there is a

problem with the test, it can be time consuming to isolate the problem. Additional tests have to be run to isolate the failure. With boundary scan, the boundary-scan cells observe device responses by monitoring the input pins of the device. This enables easy isolation of various classes of test failures, such as a pin not making contact with the circuit board.

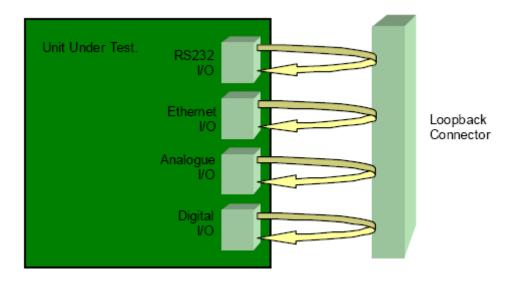

Boundary scan can be used for functional testing and debugging at various levels, from internal IC tests to board-level tests. The technology is also useful for hardware/software integration testing. For instance, Input/Output ports on a circuit card can be designed with loop-back capability. Design I/O ports so that loop-back (possibly with the addition of an external connector) is possible (see Figure 10) [12: XJTAG, 2004].

This can allow testing to be performed through any off-board connections and greatly increase test coverage. Design this facility for both analogue and digital interfaces if possible. Simple loopback connectors will suffice for most interfaces (e.g. Ethernet, RS232, RS485 etc.) but external test circuitry can aid this if necessary and this can even controlled by the TAP chain if this is extended through the I/O connector.

Figure 10. I/O Ports with loopback capability

# 5.3 In-Circuit Test Flying Probe vs. Bed-of-Nails

### 5.3.1 Bed-of Nails In-Circuit Test

In-Circuit Testing (ICT) is a process of verifying the electrical integrity of a circuit subassembly by probing test points scattered across the board's surface. It is commonly use for prototype testing as well as production testing. For automated testing, the probes are spring-loaded "pins" mounted on a thick phenolic plate and wired separately to a switching matrix. The switching matrix is an array of relays that connects the appropriate pins to the current sources and voltage-measuring instruments required at each step in the test procedure.

The phenolic plate carrying hundreds to thousands of spring-loaded pins resembles a bed of nails, and test engineers have adopted the term "bed-of-nails fixture" for the plate (see Figure 11. [1: Ed Crane, Ed Kinney and Bill Jeffrey, 1999]). Each nail is positioned so that, when the board is placed on the fixture and pulled down by a vacuum apparatus, the nail contacts its target test point without shorting to neighboring circuit structures. Figure 10 shows a typical bed-of-nails fixture. ICT can verify the existence of conducting paths, rule out the possibility of short circuits, measure individual resistors and inductors, and detect the presence and orientation of diodes, transistors and integrated circuits. ICT typically cannot determine the polarity of polarized capacitors or identify missing bypass capacitors. However, it can detect shorted capacitors and open inductors.

Basic ICT has been enhanced over the years with techniques that overcome its limitations in the face of advancing technology. For example, when integrated circuits became so large that providing probe targets for significant percentages of the circuit was impossible, ASIC engineers developed the boundary scan technique. Boundary scan provides an industry-standard method to verify device interconnects

where probe access is not present. Additional circuits designed into an IC allow the device to communicate with surrounding devices in a simple fashion and present the results of the test in an easily detectable format.

Another vectorless technique applies an AC signal through the bed of nails to the device under test. A sensor plate pressed against the top surface of the device under test forms a capacitor with the device's lead frame and couples a signal to the sensor plate. The absence of the coupled signal indicates an open solder joint. The labor needed to devise a test program for a large, complex board is monumental. Luckily, automated test program generation (ATPG) software can automatically design the required fixture and test procedure based on the PCBA's CAD data and libraries for specifications of the components placed on the board. While these techniques help reduce the program generation time, the prove-in of the high node count test program and fixture is still a time-consuming and technically challenging endeavor.

One major disadvantage of Bed-of-nails is the high cost of fixturing. A fixture is mechanical, needs maintenance, and is not easily adaptable to change. Good progress has been made in fixture cost reduction over the years, but as boards become more dense and components become more complex, the fixture becomes increasingly difficult to build, and the cost goes up again.

27

Figure 11. ICT Bed-of-Nails fixture

# 5.3.2 Flying Probe In-Circuit Test

A flying probe is an ICT that does not need a bed-of-nails fixture. Instead, several very sharp probes move over the board to perform electrical tests. Flying probe test systems are now the platform of choice for prototype testing. The most obvious and appealing attribute of the flying probe tester is the fixtureless design, eliminating the expense and time lag of ICT fixture changes. Next, and perhaps an equally important attribute, is the flexibility that the flying probe tester gives the test engineer. With a flying probe tester, engineers can take computer aided design (CAD) system data and quickly incorporate design changes into a test program, measuring the results instantaneously. This capability allows test engineers to keep pace with the ever-increasing stream of new products and product revisions.

When flying probe testers were first introduced, many of them did not have a test program generator. Test program generation on the earlier models would take an average of 3-6 days to generate and debug a new program. Today, flying probe test systems have evolved into much more sophisticated systems with extended facilities for program generation and debug, along with an extensive test portfolio.

To be an effective tool for today's electronics manufacturers, a flying probe tester should be capable of generating a complete test program for a 1000 net board in less than an hour and finish test program debugging in less than a day.

The best flying probe test systems have software that offers a variety of debugging tools, including validation of the test location, a graphical interface to change test locations, board layout and intelligent schematics tools, and menus that will show all the measurement parameters and the current measurement results. All of the board information, net information, component information and component data sheets should be available to the user.

At the end of the test program debugging, the user can compile the test program in an .exe file and protect it against change. After test program compilation, the programmer can release the test program for use by the operator.

As test and manufacturing engineers look for ways to efficiently and cost-effectively build new products, they have discovered that the flying probe tester can play a significant role in a production environment. Whether the producer is an OEM or contract manufacturer, the cost pressures are the same, and the need to employ the best test strategy is essential. Just as fixture costs have made the flying probe tester a logical choice in prototype testing, this has also become the case on the production floor. Significant throughput improvements have made flying probe testers fast enough to become an integral part of a successful test strategy.

There are many fixture-related reasons why a flying probe tester is a more logical choice than a bed of nails ICT tester. First, the space needed for test locations for a bed of nails tester has become smaller and smaller, leading to test fixtures that are more expensive and less reliable. Figure 12 shows the testing of a surface mount circuit card using flying probe [2: Gary J. Boutin, 2002]. Flying probe testers

can contact pads as small as 6 mils, vs. 25 mils for a fixture. More importantly, the available locations for test points on a fixture are diminishing, forcing the use of either an expensive double-sided fixture or a compromise in test coverage. The loss of test coverage is of critical concern and is a key motivator behind the use of flying probe test systems in production.

Figure 12. Flying Probe Testing a Printed Circuit Card

On the down side, because the flying prober is a mechanical assembly and uses moving probes rather than switching relays, it is five to 10 times slower than a conventional ICT. The average capital cost of a basic flying probe tester is nearly double that of the conventional bed-of-nails ICT. Figure 12 depicts a conventional bed-of-nails ICT.

Figure 13. Agilent 3070 In-Circuit Test

## 5.3.3 The Best of both worlds.

Both bed-of-nails and flying probe have their advantages and disadvantages. However, implementing JTAG to ICT can benefit both bed-of-nails and flying probe. Implementing JTAG with bed-of-nails can reduce the amount of pins and simplifies the fixture and yet allowing very high fault coverage of circuit card testing. Implementing JTAG with flying probe can reduce the area required for probing and thus reducing test time. However, to take advantage of the technology, the design engineers need to start their design with using JTAG in mind, which will affect the part selection, layout, etc. It is unfortunate that this author has seen circuit card designs that did not make use of this powerful tool or did not implement it correctly and rendered the debugging and boundary-scan useless. Instead of 95% fault coverage, testing was resorted to bed-of-nails which had a less than 30% fault coverage. To achieve higher fault coverage in these cases not only are costly, sometimes it is simply not feasible. Testing cannot be an after thought but an integrated part of a design.

## 5.4 Built-In-Test/Built-In-Test Equipment (BIT/BITE)

Build-In-Test is an integral capability of the system or equipment that provides an automated test capability to detect, diagnose or isolate failures. Build-In-Test is a common in both commercial and military applications. Built-In-Test Equipment is a subset of BIT. It is a device or circuit contained within a system or equipment whose primary function is to support one or more of the test modes or environments of that system or equipment or of its components [4: Raytheon IPDS, 2003].

## 5.4.1 Commercial Application – Example : OBD-II

All passenger vehicles sold in the U.S. since the Mid-90s are required to have OBD-II (On Board Diagnostic-II) system implemented. It is primarily to meet EPA emission standards, but it also provides real-time diagnostic to vehicle's failure. Failure codes are logged and can be retrieved with the appropriate reader. When an abnormal is logged, the OBD-II will inform the driver with the check-engine warning light.

Controller Area Network (CAN) Bus is the most commonly used interfaced for module-level communication in automotive application. Real time diagnostic data is transmitted on CAN Bus. A simple two-wire differential serial bus system, the CAN Bus operates in noisy electrical environments with a high level of data integrity, and its open architecture and user-definable transmission medium make it extremely flexible. Capable of high-speed (1 Mbits/s) data transmission over short distances (40 m) and low-speed (5 kbits/s) transmissions at lengths of up to 10,000 m, the multi-master CAN Bus is highly fault tolerant, with powerful error detection and handling designed in. Developed by Bosch in Germany, CAN Bus was originally designed specifically for the automotive market, which remains its primary application area today [7: CAN Bus in Automation, 2004]. The actual diagnostic functionality, however, has to be implemented at the module level with firmware and/or software.

## 5.4.2 Military Application – A case study: Bradley A3

BIT is extensively used in military applications as well. In the article "Effects of Built-In-Test/Built-In-Test Equipment for A3 Bradley Improved Bradley Acquisition System (IBAS)", Suzanne Birdsong stated the benefits for a well design BIT/BITE in a complex system [3: Suzanne Birdsong, 2001]. The following is the case study on the A3 Bradley. The Bradley Fighting Vehicle System (BFVS) A2 and prior models required the use of extensive diagnostic test equipment to troubleshoot and repair its subsystems. The result was a Mean-Time-To-Repair (MTTR) higher than desired for a combat vehicle that had a high readiness requirement. MTTR, simply puts, is how quickly and easily the system can be fixed.

The BFVS A3, the predecessor of the BFVS A2, was upgraded with the Improved Bradley Acquisition System (IBAS). The IBAS serves as the main sighting subsystem for the BFVS and the fire control for the TOW missile system and guns. It houses an Infrared detector for night vision, a daytime camera, xenon beacon tracker for TOW guidance, direct view optics and a laser range finder. While the IBAS increased the capability of the A3, the complexity of the subsystem also had the potential to decrease MTTR, the vehicle readiness and increase life-cycle costs. To mitigate this risk, one of the major enhancements of the A3 is the integrated maintenance diagnostics and Built-In-Test/Built-In-Test Equipment. In addition, the reliability, availability, and maintainability (RAM) policy in DOD 5000.2, states that RAM issues should be addressed early in the acquisition cycle to meet operational requirements to reduce life-cycle costs.

To meet the RAM policy in DOD 5000.2, the Close Combat Anti-Armor Weapons Program Management Office (CCAWS PMO) incorporated a "bottoms up" approach. The CCAWS PMO required the IBAS contractor, Texas Instruments (Note: The defense division of TI was acquired by Raytheon Company in 1997), to address and incorporate BIT/BITE as part of the design starting at the

circuit board level. For example, each circuit board was required to have some sort of BIT/BITE and was addressed at each design review. Texas Instruments (TI) was also tasked to eliminate the 180 day preventive maintenance required on the sighting system for the BFVS-A2. To accomplish this, TI was given the 180 day Verification Test Maintenance Manual for the A2 and told to embed BIT/BITE capabilities into the subsystem. An example of what TI was able to accomplish is the internal targets for the sensors (FLIR, Xenon Beacon, day camera and DVO). In order to determine the condition of the subsystems. This piece of test equipment was cumbersome to use and required intense man-hours to set up and use. With the internal targets built into the IBAS, this piece of test equipment was eliminated. The IBAS was capable of testing itself using the internal targets and notifying the operator of the condition of the unit. Not only did the IBAS eliminate a piece of test equipment but this test does not require a specialized skill.

BIT/BITE can be a cost driver. In order to determine the amount of BIT/BITE necessary to meet the users needs, CCAWS PMO used the BFVS-A3 Failure Modes, Effects and Criticality Analysis (FMECA) for the sighting subsystem. The FMECA is a procedure that analyzes each potential system failure mode to determine its results or effects on the system and to classify each potential failure mode according to its severity. The purpose is to provide a safer and more reliable initial design. The FMECA also helps to identify single points of failure that show how the failure of one component can cause the failure of the entire subsystem. Through the use of the FMECA, TI was able to identify what BIT/BITE was needed to meet the BFVS requirements and save cost that could have been incurred by developing unnecessary BIT/BITE.

Because of the early focus on maintainability during the IBAS development, key features such as BIT/BITE were implemented into the subsystem design to reduce the maintenance hours and test equipment. The obstacle that was faced by an early focus on maintainability was resistance by those personnel who had been accustomed to waiting until later in the development cycle to address logistics. In development of systems and subsystems, most of the focus is on making the system meet the mission requirement and putting off the support issues until later. It was only through the dedication and persistence of the logistic community, and an unusual relationship with engineering, that the development of BIT/BITE was given the same priority as the mission requirements. The lesson learned was that early focus on logistics has a significant impact on the maintainability of the system throughout its life cycle.

It is important that logistical issues be addressed early in the life cycle of a system. During the development, logistical issues must be given the same priority as the system mission requirements. Program Managers must be made to understand that the cost incurred up front for logistics equals a savings later in the life cycle. The PM must also understand that by addressing logistics up front there is greater potential of reducing the MTTR and increasing the Operational Availability of the system. The BFVS-A3 was able to accomplish a reduction in MTTR by eliminating test equipment and replacing it with BITE and incorporating BIT.

## CHAPTER VI DESIGN FOR TESTABILITY

#### 6.1 Design For Testability (DFT)

A quick search on the Internet reveals many hits on key words "Design for Testability". Many of those hits are from various universities and educational institutes. Courses are offered on the subject of Design for Testability, mostly under the department on Electrical/Electronics and Computer Engineering. Many companies offer consulting services and turn-key solution in Design for Testability as well. Integrated Circuit (IC) manufacturers are leading in the research and application of Design for Testability. Due to the high volume nature of IC's production, IC manufacturers have to verify the chip design and test 100% of their products. Any manufacturing defects and more importantly design defects have to be caught before the product is out on the market. Failing to do so not only extremely is costly financially but can also negatively impact a company's reputation. In 1994 the Floating Point Division (FDIV) bug in Intel Pentium CPU not only was a tremendous cost to Intel financially; it also generated a lot of negative publicity. With rival Advanced Micro Devices (AMD) gaining market share, that kind of publicity was really costly to Intel reputation.

The cost of fabricating an IC continues to fall as fabrication process advances. However, the Cost of Test (COT) keeps rising due to the increase in complexity, especially for System-on-a-Chip (SOC) devices. Cost of Test becomes an increasing portion of semiconductor device manufacturing cost. According to the white paper "Reducing Cost of Test Through DFT" by Agilent Technologies [16: Agilent Technologies, 2004], a Design for Testability solution must span the entire System on a Chip development process from design to high volume test to realize the potential Cost of Test and Time to Market (TTM) savings. Figure 14 illustrates the SOC development process, using an example of the cores that might comprise a DVD SOC.

**Figure 14. SOC Development Process**

Advanced IC design and manufacturing is one of the most technically challenged industries. IC manufacturers need keep pace with Moore's law and with the continued density and performance improvements delivered by IC process technology. Realizing the benefits and cost saving of design for testability, significant investment is made by IC manufacturers during the design flow to ensure testability. According to the white paper, design for testability can account for as much as 50% of the total design cost. There are several factors to take into account in the design phase:

- Design engineering time spent to ensure testability by incorporating DFT techniques

- Licensing charges for third party DFT IP to be integrated into the SOC

- Cost of chip real estate used for DFT.

- Test engineer's time to bring a device into manufacturing.

- Cost of capital equipment and the necessary services and support to support the test engineers.

- Cost to spin a device if the first design doesn't work, which includes:

- Re-design the part

- Cost of a new set of masks

- Cost to run a new batch of silicon.

These factors, with a few exceptions, are applicable to any product that involves hardware design and development.

# **6.2 DFT Process**

As systems become more and more complex, the days when design, test and production could afford to be isolated entities have been long gone. Designs cannot be complete to the functional requirement and then "*thrown over the wal*"l. In order to meet cost and schedule constraints, the development of a product must involve collaboration between the different entities. This collaboration must begins in the earliest stages of a product's conception and be ongoing. Design, hardware, software, test and production engineers must bring their own expertise and experience as well as their own goals to the table in order to truly driving for a successful product.

Design for testability addresses the need to: 1) collect data during the development process concerning particular performance characteristics; 2) enable efficient and economical production by providing ready access to, and measurement of, appropriate acceptance parameters; and 3) enable rapid and accurate assessment of the status of the product to the lowest repairable element when deployed. Many hardware systems have testing circuits designed and built-in. This early planning by design engineers allows easy testing for fault isolation of circuits, both in system development phases and during operational testing and deployment.

The design for testability process typically involves the following steps (see Figure 14):

- 1. Define testability objectives

- 2. Select testability techniques to influence design

- 3. Conduct trade studies

- 4. Check testability

- 5. Verify whether design meets testability needs. If not, repeat steps 2 through 4.

Figure 15. Process for Design for Testability

The testability objectives can include fault coverage, accessibility, reliability, isolation, interfacing with test equipment, etc. The proper testability techniques should be selected to influence the design. Trade studies are to be conducted to balance between cost and effectiveness. Finally an analysis is required to see if the design meets the testability needs. This process provides a guideline and is to be implemented with flexibility. All of the techniques and technologies described in Chapter 5 can be applied to step 2. These techniques and technologies will be obsolete someday. As new techniques and technologies are available, they should be applied accordingly.

# CHAPTER VII Raytheon Integrated Product Development System (IPDS)

# 7.1 Introduction

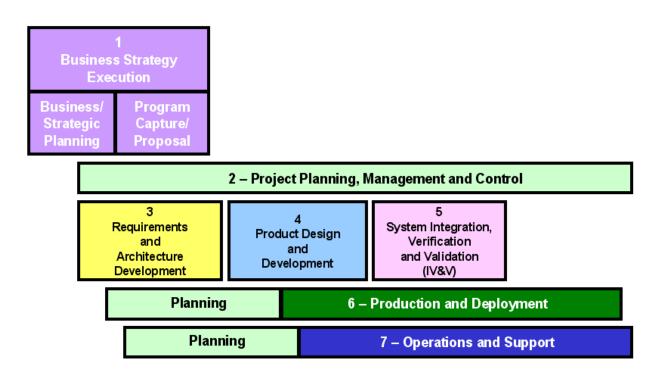

The Raytheon Integrated Product Development System (IPDS) is a common process to support program management and engineering development throughout the product life cycle, from program pursuit to definition to design and production [4: Raytheon IPDS, 2003]. The purpose of IPDS is to enhance Raytheon customer's success and to provide the discipline necessary for program predictability, performance, and reliability. Raytheon IPDS has a collection of processes, discipline sub-processes, methods, tools, training and best practices. Figure 16 is a pictorial view of the IPDS structure.

# Figure 16. Structure of Integrated Product Development System

IPDS is truly a "system" of processes. Within the structure of IPDS are the following components:

• Integrated Product Development Process (IPDP)

- Product Processes

- Discipline Processes

- Methods and Tools

- Process Management

Integrated Product Development Process (IPDP) describes "the way Raytheon do business" in general, on all programs. Product Processes integrate Discipline Processes into a process used to produce a specific product (e.g. an Antenna or a PGA). Discipline Processes describe a set of activities disciplines perform that are common across several products (e.g. Systems Engineering or Software Development). Methods describe "how" to perform detailed processes (e.g. Risk Analysis, Thermal Analysis, etc.). Tools automate execution of the processes (e.g. CAD/CAM). Process Management Processes describes "how" to deploy and manage all the processes in IPDS.

In May 1995, consistent with the Department of Defense (DoD) efforts to implement best commercial practices, the Secretary of Defense directed "a fundamental change in the way the Department acquires goods and services. The concepts of Integrated Product and Process Development (IPPD) and Integrated Product Teams (IPT) shall be applied throughout the acquisition process to the maximum extent practicable."

IPPD evolved in industry as an outgrowth of efforts such as Concurrent Engineering to improve customer satisfaction and competitiveness in a global economy. During the summer of 1995, the Office of the Secretary of Defense (OSD) surveyed over 80 government and industry organizations regarding their IPPD policies and practices. Using those survey results, OSD published the DoD Guide to Integrated Product and Process Development (Version 1.0), dated February 5, 1996. The DoD Guide to IPPD was developed to provide a general understanding of DoD's perspective on IPPD. DoD defines IPPD as "a management technique that simultaneously integrates all essential acquisition activities through the use of multidisciplinary teams to optimize the design, manufacturing and supportability

processes." There are basically ten tenets for IPPD listed as follow (see description of the tenets in Appendix C):

- 1. Customer Focus

- 2. Concurrent Development of Product and Processes

- 3. Early and Continuous Lifecycle Planning

- 4. Maximize Flexibility for Optimization and Use of Contractor Approaches