# **BIT Analysis Process**

# Systems Engineering Master's Project

# Davinia B. Chism

Submitted to the College of Engineering Texas Tech University in Partial Fulfillment Of the Requirements for The Degree of MASTER OF ENGINEERING

October 12, 2002

Approved:

Dr. J. Borrelli

Dr. A. Ertas

Dr. T. Maxwell

Dr. M. Tanik

# Abstract

Most products developed and marketed today need to be of high quality, easily maintainable and robust. As a result, product specifications have requirements for a system level built-in test (BIT). These requirements cover BIT detection percentages, false alarm rates, fault isolation percentages and other parameters to be measured at a system level.

The objective of this project is to develop a process to perform an analysis of the BIT on an existing system to determine the failure detection and fault isolation percentages and false alarm rates. An easy to follow process, adaptable to any system, and automated tools to simplify equations are a part of this process.

As an example and the test system for the process, this project includes a BIT analysis on the HTI Second Generation Forward Looking Infrared (FLIR) sensor. The HTI FLIR is an existing design that has BIT tests implemented and specific requirements for failure detection percentages and false alarm rates. An analysis was performed early in the program on a previous design and no re-analysis of the system has taken place. Prior to the conclusion of this project, the HTI program had no way of verifying these BIT requirements.

## Acknowledgements

I would like to thank Dr. Ertas and Dr. Tanik for their enthusiasm and support in my goal of pursuing this degree. They both opened my eyes – not only to new topics and information – but also to the concept of pursuing topics and synthesizing the new from the traditional. I have admired their selfless devotion of time to us, the many respected educators and industry professionals they have shared with us, and their sincere interest in providing us the best education and skills to last a lifetime.

I would also like to acknowledge Greg Norby and Hector Reyes. They have supported me at Raytheon while I worked through this program and balanced the requirements of my job with school-work. They offered invaluable advice and I am grateful for the help and encouragement they gave me.

Thanks to my group members, Jean Cathcart, Kurt Himmelreich and Donna Maestas. We made a strong team and learned a great deal working together. Special thanks to Jean who helped me keep my sanity at work and in school.

My family deserves my undying thanks and love for supporting me and understanding the limitations on my time. Their belief in my goals and me means everything.

# Disclaimer

This report is a generic approach to analyzing the Built-in-Test capabilities of an existing system. The opinions expressed in this paper are strictly those of the author and are not necessarily those of Raytheon, Texas Tech University, nor any U.S. Government agency.

### **Table of Contents**

| CHAPTEI                                                                                                           | 1 INTRODUCTION                                                                                                                                                                                                                                                                        | 1  |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 B                                                                                                             | T REQUIREMENTS FOR ROBUSTNESS AND MAINTAINABILITY                                                                                                                                                                                                                                     | 1  |

|                                                                                                                   | E PROJECT GOAL IS TO SIMPLIFY THE PROCESS                                                                                                                                                                                                                                             |    |

| 1.3 Ph                                                                                                            | OCESS REQUIREMENT 1 - DATA GATHERING                                                                                                                                                                                                                                                  | 2  |

| 1.4 Pr                                                                                                            | OCESS REQUIREMENT 2 - DATA PROCESSING                                                                                                                                                                                                                                                 | 2  |

|                                                                                                                   | OCESS REQUIREMENT 3 - DATA REPORTING                                                                                                                                                                                                                                                  |    |

|                                                                                                                   | IAL RUN ON HTI                                                                                                                                                                                                                                                                        |    |

| 1.7 Co                                                                                                            | NCLUSION: GENERIC PROCESS                                                                                                                                                                                                                                                             | 3  |

| CHAPTEI                                                                                                           | 2 BACKGROUND                                                                                                                                                                                                                                                                          | 4  |

| 2.1 Pt                                                                                                            | RPOSE OF BIT                                                                                                                                                                                                                                                                          | 4  |

| 2.2 Bl                                                                                                            | T REQUIREMENTS – DEFINITIONS                                                                                                                                                                                                                                                          | 5  |

| 2.3 Co                                                                                                            | MMON BIT REQUIREMENT VERIFICATION METHODS                                                                                                                                                                                                                                             | 7  |

| 2.3.1                                                                                                             | Who Performs BIT Requirements Verification?                                                                                                                                                                                                                                           |    |

| 2.3.2                                                                                                             | BIT Requirements Verification in the System Development Process                                                                                                                                                                                                                       |    |

|                                                                                                                   | FFICULTY OF VERIFYING REQUIREMENTS ON EXISTING SYSTEMS                                                                                                                                                                                                                                |    |

| 2.4.1                                                                                                             | Adverse Factors in Existing Designs                                                                                                                                                                                                                                                   |    |

|                                                                                                                   | SCRIPTION OF HTI SYSTEM                                                                                                                                                                                                                                                               |    |

|                                                                                                                   | T REQUIREMENTS ON HTI                                                                                                                                                                                                                                                                 |    |

|                                                                                                                   | SCRIPTION OF THE NEED FOR BIT ANALYSIS ON HTI                                                                                                                                                                                                                                         |    |

| 2.7.1                                                                                                             | Original Analysis Results                                                                                                                                                                                                                                                             |    |

| 2.7.2                                                                                                             | Modification of Original Data                                                                                                                                                                                                                                                         |    |

| 2.7.3                                                                                                             | Current HTI BIT Analysis Status                                                                                                                                                                                                                                                       |    |

| CHAPTEI                                                                                                           | 3 ANALYSIS                                                                                                                                                                                                                                                                            |    |

| 3.1 B                                                                                                             | T STATISTICAL METHODS                                                                                                                                                                                                                                                                 |    |

| 3.1.1                                                                                                             | Definitions                                                                                                                                                                                                                                                                           |    |

| 3.1.2                                                                                                             | Functional Reliability versus Component Reliability                                                                                                                                                                                                                                   | 21 |

| 3.1.3                                                                                                             | System Mapping – Functions to Components                                                                                                                                                                                                                                              |    |

| 3.1.4                                                                                                             | Failure Types in Functional Reliability Analyses                                                                                                                                                                                                                                      |    |

| 3.1.5                                                                                                             | Failure Rate versus Failure Probabilities                                                                                                                                                                                                                                             |    |

| 3.1.6                                                                                                             | FMEA/FMECA                                                                                                                                                                                                                                                                            |    |

|                                                                                                                   | T REQUIREMENT CALCULATIONS                                                                                                                                                                                                                                                            |    |

| 3.2.1                                                                                                             | Fault Detection Calculation                                                                                                                                                                                                                                                           |    |

| 2 2 2 2                                                                                                           | Fault Isolation Calculation                                                                                                                                                                                                                                                           |    |

| 3.2.2                                                                                                             |                                                                                                                                                                                                                                                                                       | 26 |

| 3.2.3                                                                                                             | False Alarm Rate Calculation                                                                                                                                                                                                                                                          |    |

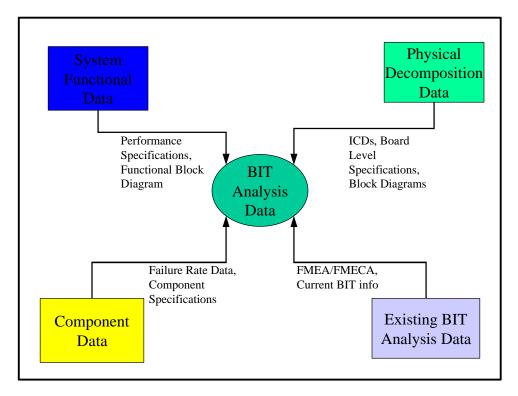

| 3.2.3<br>3.3 T                                                                                                    | PES OF DATA NEEDED                                                                                                                                                                                                                                                                    |    |

| 3.2.3<br>3.3 T<br>3.3.1                                                                                           | PES OF DATA NEEDED<br>System Functional Data                                                                                                                                                                                                                                          | 37 |

| 3.2.3<br>3.3 Tr<br>3.3.1<br>3.3.2                                                                                 | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data                                                                                                                                                                                                           |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3                                                                         | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data                                                                                                                                                                                         |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                                                                | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data                                                                                                                                                   |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D                                                       | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES                                                                                                                                |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D<br>3.5 D                                              | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES<br>TA PROCESSING AND ANALYSIS                                                                                                  |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D<br>3.5 D<br>3.5.1                                     | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES<br>TA PROCESSING AND ANALYSIS<br>Complete the FMEA                                                                             |    |

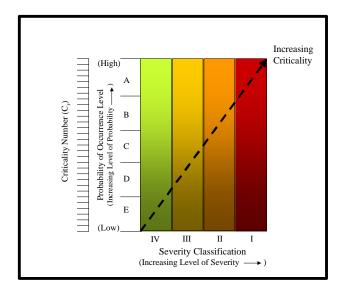

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D<br>3.5 D<br>3.5.1<br>3.5.1<br>3.5.2                   | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES<br>TA PROCESSING AND ANALYSIS<br>Complete the FMEA<br>Perform the Criticality Analysis                                         |    |

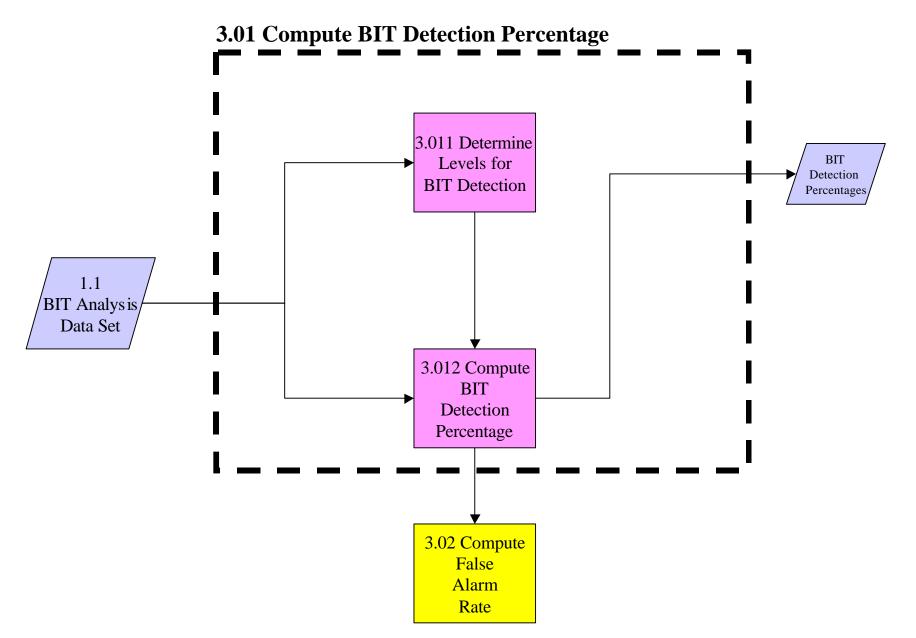

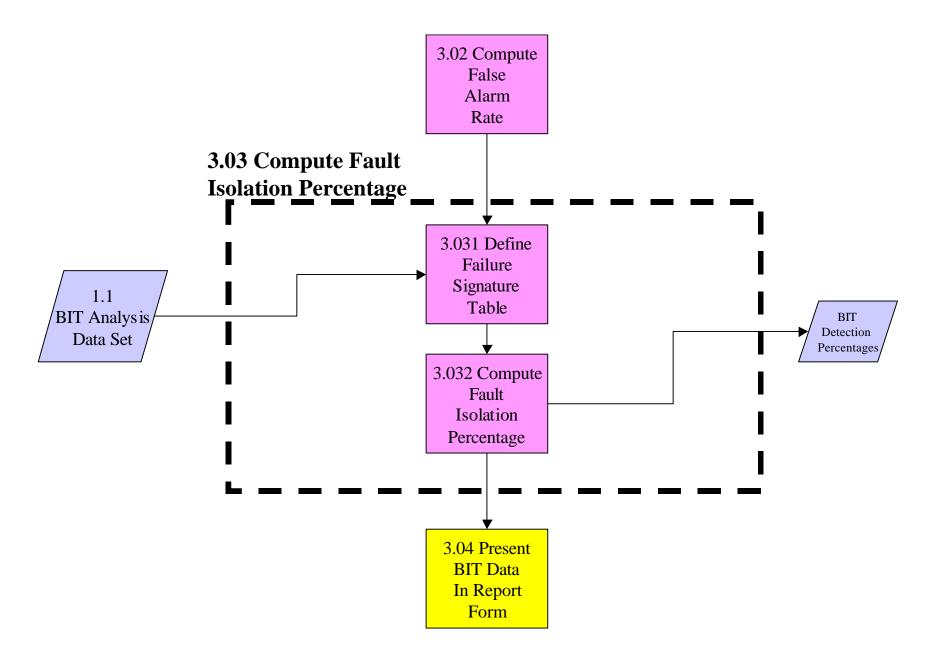

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D<br>3.5 D<br>3.5.1<br>3.5.2<br>3.5.1<br>3.5.2<br>3.5.3 | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES<br>TA PROCESSING AND ANALYSIS<br>Complete the FMEA<br>Perform the Criticality Analysis<br>Perform BIT Requirement Calculations |    |

| 3.2.3<br>3.3 T<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4 D.<br>3.5 D.<br>3.5.1<br>3.5.2<br>3.5.3<br>3.6 D.       | PES OF DATA NEEDED<br>System Functional Data<br>Physical Decomposition Data<br>Component Data<br>Existing Reliability Analysis Data<br>TA ALTERNATIVES<br>TA PROCESSING AND ANALYSIS<br>Complete the FMEA<br>Perform the Criticality Analysis                                         |    |

| 3.7.1                                                                                    | Advanced Specialty Engineering Networked Toolkit (ASENT)                                                                                                                                                                                                                                                                                                       | 45                    |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

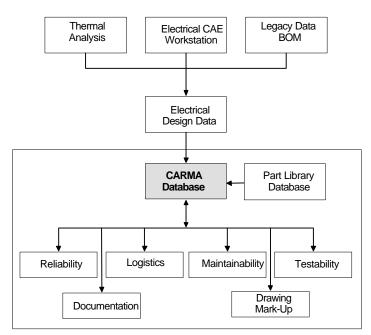

| 3.7.2                                                                                    | Computer Aided Reliability and Maintainability Applications (CARMA) Toolkit                                                                                                                                                                                                                                                                                    | 46                    |

| 3.7.3                                                                                    | RAM Commander                                                                                                                                                                                                                                                                                                                                                  |                       |

| CHAPTER                                                                                  | 4 COMPARISONS                                                                                                                                                                                                                                                                                                                                                  | 51                    |

| 4.1 Fr                                                                                   | val Process                                                                                                                                                                                                                                                                                                                                                    | 51                    |

| 4.2 AP                                                                                   | PLICATION OF PROCESS TO HTI                                                                                                                                                                                                                                                                                                                                    | 53                    |

| 4.2.1                                                                                    | Assumptions                                                                                                                                                                                                                                                                                                                                                    |                       |

| 4.3 DA                                                                                   | TA RESULTS                                                                                                                                                                                                                                                                                                                                                     | 56                    |

| 4.4 AN                                                                                   | VALYSIS OF RESULTS                                                                                                                                                                                                                                                                                                                                             | 57                    |

| 4.5 As                                                                                   | SESSMENT OF PROCESS                                                                                                                                                                                                                                                                                                                                            | 58                    |

| 4.5.1                                                                                    | Ease of Use                                                                                                                                                                                                                                                                                                                                                    | 58                    |

| 4.5.2                                                                                    | Time Savings                                                                                                                                                                                                                                                                                                                                                   | 59                    |

| 4.5.3                                                                                    | Tailorability                                                                                                                                                                                                                                                                                                                                                  | 59                    |

| 4.5.4                                                                                    | Tool Usage                                                                                                                                                                                                                                                                                                                                                     | 59                    |

| 4.5.5                                                                                    | Verifies BIT Requirements                                                                                                                                                                                                                                                                                                                                      |                       |

| 4.5.6                                                                                    | Clarity of Directions                                                                                                                                                                                                                                                                                                                                          | 60                    |

| 4.5.7                                                                                    |                                                                                                                                                                                                                                                                                                                                                                | <b>C</b> 0            |

| 4.3.7                                                                                    | Cost Savings                                                                                                                                                                                                                                                                                                                                                   | 60                    |

|                                                                                          | Cost Savings                                                                                                                                                                                                                                                                                                                                                   |                       |

| CHAPTER                                                                                  | C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                          | 62                    |

| CHAPTER<br>5.1 BE                                                                        | 5 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                  | <b>62</b>             |

| <b>CHAPTER</b><br>5.1 BE<br>5.2 AP                                                       | 8 5 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                | <b>62</b><br>62<br>62 |

| <b>CHAPTER</b><br>5.1 BE<br>5.2 AP                                                       | 2 5 CONCLUSIONS<br>NEFITS OF THE PROCESS<br>PLICABILITY TO ANY PROGRAM                                                                                                                                                                                                                                                                                         |                       |

| <b>CHAPTER</b><br>5.1 BE<br>5.2 AP<br>5.3 DE                                             | <b>5 CONCLUSIONS</b><br>NEFITS OF THE PROCESS<br>PLICABILITY TO ANY PROGRAM<br>SCUSSION OF SYSTEMS ENGINEERING/TRANSDISCIPLINARY PROCESS                                                                                                                                                                                                                       |                       |

| CHAPTER<br>5.1 BE<br>5.2 AP<br>5.3 DE<br>5.3.1<br>5.3.2                                  | <b>5 CONCLUSIONS</b><br>NEFITS OF THE PROCESS<br>PLICABILITY TO ANY PROGRAM<br>SCUSSION OF SYSTEMS ENGINEERING/TRANSDISCIPLINARY PROCESS<br>Application of Transdisciplinary Process to Project                                                                                                                                                                |                       |

| CHAPTER<br>5.1 BE<br>5.2 AP<br>5.3 DE<br>5.3.1<br>5.3.2<br>CHAPTER                       | <b>5 CONCLUSIONS</b><br>NEFITS OF THE PROCESS<br>PLICABILITY TO ANY PROGRAM<br>SCUSSION OF SYSTEMS ENGINEERING/TRANSDISCIPLINARY PROCESS<br>Application of Transdisciplinary Process to Project<br>Transdisciplinary Process in the BIT Analysis Process                                                                                                       |                       |

| CHAPTER<br>5.1 BE<br>5.2 AP<br>5.3 DE<br>5.3.1<br>5.3.2<br>CHAPTER<br>CHAPTER            | <ul> <li>5 CONCLUSIONS</li> <li>NEFITS OF THE PROCESS</li> <li>PLICABILITY TO ANY PROGRAM</li> <li>SCUSSION OF SYSTEMS ENGINEERING/TRANSDISCIPLINARY PROCESS</li> <li>Application of Transdisciplinary Process to Project</li> <li>Transdisciplinary Process in the BIT Analysis Process</li> <li>6 REFERENCES</li> </ul>                                      |                       |

| CHAPTER<br>5.1 BE<br>5.2 AP<br>5.3 DE<br>5.3.1<br>5.3.2<br>CHAPTER<br>CHAPTER<br>CHAPTER | <ul> <li>5 CONCLUSIONS</li> <li>NEFITS OF THE PROCESS</li> <li>PLICABILITY TO ANY PROGRAM</li> <li>SCUSSION OF SYSTEMS ENGINEERING/TRANSDISCIPLINARY PROCESS</li> <li>Application of Transdisciplinary Process to Project</li> <li>Transdisciplinary Process in the BIT Analysis Process</li> <li>6 REFERENCES</li> <li>7 APPENDIX I – NOMENCLATURE</li> </ul> |                       |

| CHAPTER<br>5.1 BE<br>5.2 AP<br>5.3 DE<br>5.3.1<br>5.3.2<br>CHAPTER<br>CHAPTER<br>CHAPTER | <ul> <li>5 CONCLUSIONS</li></ul>                                                                                                                                                                                                                                                                                                                               |                       |

## List of Figures

| .7 |

|----|

| 11 |

| 12 |

| 15 |

| 22 |

| 23 |

| 25 |

| 25 |

| 27 |

| 31 |

| 34 |

| 38 |

| 46 |

| 47 |

| 49 |

| 52 |

|    |

### List of Tables

| TABLE 1. COMMON BIT REQUIREMENT VERIFICATION METHODS                            | 8  |

|---------------------------------------------------------------------------------|----|

| TABLE 2. HTI BIT DETECTION AND ISOLATION REQUIREMENTS AND PREDICTED PERFORMANCE | 17 |

| TABLE 3. B-KIT FAILURE RATE ADJUSTMENTS – ORIGINAL BIT ANALYSIS                 | 18 |

| TABLE 4. FUNCTIONAL DECOMPOSITION                                               | 24 |

| TABLE 5. QUALITATIVE APPROACH CLASSES                                           | 29 |

| TABLE 6. COMMON FAULT SIGNATURE GROUPINGS                                       | 36 |

| TABLE 7. SAMPLE DATA TABLE FOR REPORT.                                          | 44 |

| TABLE 8. ASSEMBLY LEVELS ANALYZED                                               | 56 |

| TABLE 9. HTI BIT DETECTION AND ISOLATION REQUIREMENTS FROM THE NEW ANALYSIS     | 58 |

# CHAPTER 1 INTRODUCTION

#### 1.1 BIT Requirements For Robustness and Maintainability

Most products developed and marketed today not only need to be of high quality, but also need to be well maintained and robust. As a result, product specifications have requirements for a system level built-in test (BIT). These requirements cover BIT detection percentages, false alarm rates, fault isolation percentages and other parameters to be measured at a system level. The BIT tests facilitate maintainability and robustness by correctly identifying system failures. All hardware related functionality is covered by the tests and thus BIT can provide an accurate assessment of system operability.

Successful completion of the BIT tests after power-up serves as an indicator that the system is fully functional. If the BIT tests are incomplete or ill-defined and do not test a portion of the system, then the 'pass' indicator may be a false indication of system health. Similarly, if the tests fail when the system is not broken, the indicator wrongly declares the system inoperable. Responsibility lies on the system designer to verify the BIT tests fully and correctly test system functionality. BIT analyses are performed to prove the BIT tests meet the customer requirements.

As more and more emphasis is placed on developing quality products that can be maintained and as improvements are made to existing designs, the need for robust self-tests is increased. Customers are requiring designers to detect a certain percentage of failures – accurately. As the designers develop these BIT tests, it becomes increasingly difficult to prove to the customer that they meet the requirement for false alarm rates, detection percentages and isolation percentages. In most cases the designers will implement BIT tests based on a BIT analysis performed on the initial design and incrementally improve the BIT based on trial and error. The BIT analysis for detection percentages, isolation percentages and false alarm rates is not performed at all. It is too difficult and time consuming.

#### **1.2** The Project Goal is to Simplify the Process

The purpose of this project is to develop a process to perform an analysis of the BIT on an existing system. New designs will not be considered to reduce the scope of the project and because the more difficult, and common, task is to analyze a system that has already been designed. The analysis will determine the failure detection percentages, fault isolation percentages and false alarm rates of the BIT implemented on the current system. The process developed in this project will include an easy to follow process, adaptable to any system, and automated tools to simplify equations and data gathering. The final product of this project is a BIT Analysis Process. The BIT Analysis Process is a standardized process to aid an engineer in determining the BIT detection percentage and false alarm rates for an existing product and create a report of the results.

#### 1.3 Process Requirement 1 - Data Gathering

One of the most difficult tasks in verifying BIT requirements, especially on an existing design, is sorting through volumes of program data. Very specific information is needed to verify the requirements. The goal is to minimize the data gathering effort so the appropriate data can be sought and irrelevant data ignored. The BIT Analysis Process provides a standardized data gathering technique/template.

#### 1.4 Process Requirement 2 - Data Processing

The analysis of the data is the stage where verification of the BIT requirements takes place. After the appropriate data has been gathered, system functionality and configuration is analyzed to determine the full set of operations to be tested. Using this information, the data is applied to equations to calculate the numbers for BIT detection, fault isolation and false alarm rates specified in the requirements. The BIT Analysis Process will provide a tool to process the data and calculate the numbers specified by the BIT requirements.

#### 1.5 Process Requirement 3 - Data Reporting

Verification of the BIT requirements requires documented proof. The data gathered and analyzed in the BIT Analysis Process must be presented in a form that provides sufficient information to prove the verification/validation of BIT requirements. The BIT Analysis Process will provide a method to output the results of the calculations in such a manner to show how the results were generated and provide validity to the results.

#### **1.6 Trial Run on HTI**

As an example and the test system for the process, this project will include a BIT analysis on the HTI Second Generation Forward Looking Infrared (FLIR) sensor. The HTI FLIR is an existing design that has BIT tests implemented and specific requirements for failure detection percentages, fault isolation percentages and false alarm rates. An analysis was performed early in the program on a previous design and no re-analysis of the system has taken place. The program currently has no way of verifying these requirements.

#### 1.7 Conclusion: Generic Process

In conclusion, the project will create a BIT Analysis Process that is a standardized process to verify BIT requirements on an existing system. It will be used on one program, as an example, to verify its reliability but will be adaptable to other programs.

# CHAPTER 2 BACKGROUND

#### 2.1 Purpose of BIT

Built-in-Test (BIT) can generally be described as a set of evaluation and diagnostic tests that uses resources that are an integral part of the system under test. [Drees, 2002] Historically, a lack of attention and standards by professional and academic associations has led to confusion over the role of BIT. The lack of standardization is responsible for various different definitions of BIT at numerous system levels. The assorted definitions contribute to the confusion over the specific role of BIT. However, the role of BIT and its usefulness, at all levels, has been recognized in electronic equipment as early as the 1950s. [Goodman, 1967]

The role of BIT was originally designed to ensure uninterrupted availability and fault free operation of critical weapon systems (Minutemen I and II missiles) and aerospace equipment (Saturn, Apollo). [Pecht, 2001] BIT is also used for in-field maintenance by the end user, to indicate system status, and to indicate whether a system has been assembled properly. As a result, BIT has been used in diverse applications including oceanographic systems, multi-chip modules, large-scale integrated circuits, power supply systems, avionics, and even passenger entertainment systems for the Boeing 767. [Pecht, 2001] Although the general concept of BIT remains the same, each specific field has its own specialties and adaptations. [Gao, 2001]

The role of BIT in electronic systems has grown in prominence with the advances in system complexity and concern over maintenance lifecycle costs of large systems. Today, in an environment where standards drive systems designs (and provide an avenue for focused advancement in technology), standards for BIT are finally evolving. The reasons for advancing the effectiveness of BIT include reduced overhead for support, greater confidence in operation, and increased system availability. [Drees, 2002]

With the increase in the importance of the role of BIT and the development of standards for BIT comes the development of BIT requirements on programs. The cost of supporting military electronic systems (avionics, communications, and weapons systems) has driven much of the development in BIT technology and requirements development. There has also been a beneficial effect on the maintenance and availability of test and measurement instrumentation, Automatic Test Equipment (ATE), due to the requirement for BIT in their component assemblies. BIT has found a role in all program phases including Design Verification Test, Integration Verification and Validation, Hardware Integration, Hardware-Software Integration, System Integration, Verification and Validation, System Qualification and Reliability Testing, Factory, Production and Depot Test, and Field Support. [Sallade, 1999] But as the role of BIT becomes a requirement, a new need is created: a method to verify the BIT requirements.

#### **2.2 BIT Requirements – Definitions**

Several definitions of BIT, based on the system level at which they are executed, exist. Requirements for BIT are generally in the form of specific values for BIT detection percentages, fault isolation percentages and false alarms rates. Definitions for the key BIT requirement terms are below:

| BIT                  | Built in Test – An on-board hardware/software diagnostic<br>means to identify and locate faults. It includes error detection<br>and correction circuits, totally self-checking circuits and self-<br>verification circuits. [Drees, 2001]                            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT Detection        | Proportion of system failures detected automatically by BIT.<br>The higher the BIT detection percentage, the better the<br>capability. [Giordano, 2001]                                                                                                              |

| BIT False Alarm      | Alarms that occur during system operation but cannot be later duplicated. [Steinmetz, 2002]                                                                                                                                                                          |

| BIT Fault Isolation  | Isolating a failure by BIT to a subsystem or lower level part.<br>Generally in terms of fault isolating to one item X% of the time<br>and N or fewer items Y% of the time. The higher the fault<br>isolation percentage, the better the capability. [Giordano, 2001] |

| CBIT                 | Continuous BIT. Equipment is monitored continuously and automatically without affecting normal operation. [Pecht, 2001]                                                                                                                                              |

| Fault                | Erroneous state of hardware or software resulting from failures<br>of components, physical interference from the environment,<br>operator error or incorrect design. [Siewiorek, 1982]                                                                               |

| Fault Detection Time | The time which elapses between the occurrence of a fault and the detection (reporting) of the fault by BIT. [MIL-STD-2165, 1989]                                                                                                                                     |

| Fault Location       | Physical points within the design which are subject to failure.<br>Fault locations can be detectable, non-detectable, or excluded<br>from system consideration (minimal impact to system<br>functionality). [Giordano, 2001] |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBIT                 | Interruptive BIT. Normal equipment operation is suspended<br>while test take place. IBIT normally occurs at power up or is<br>initiated by the operator. [Pecht, 2001]                                                       |

| Instrument Level BIT | Module/Assembly level BIT. BIT is performed on Module<br>level and Line Replacable Units (LRUs) that are unique<br>electronic assemblies comprising of one or more circuit card<br>assemblies. [Drees, 2001]                 |

| PBIT                 | Periodic BIT. An IBIT which interrupts normal operations periodically in order to carry out a pseudo-continuous monitoring function. [Pecht, 2001]                                                                           |

| Self Test BIT/ BIST  | Built in Self-Test. Circuit level tests – BIT techniques applied to circuit cards using digital and analog methods. [Drees, 2001]                                                                                            |

| System Level BIT     | System level self-test. BIT based upon the similarity of high-<br>level requirements and concerns such as: BIT detection<br>percentage, execution time, false alarm rates, and fault<br>isolation. [Drees, 2001]             |

| Test                 | A routine that stimulates a portion of the circuitry, measures the response, and then compares the result to a known or desired value. [Giordano, 2001]                                                                      |

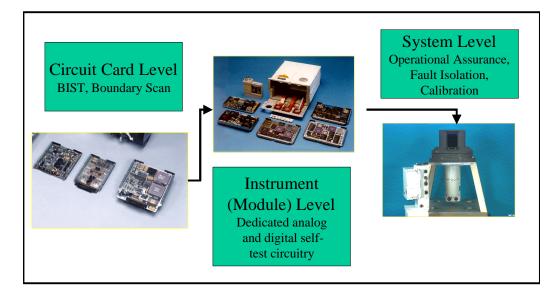

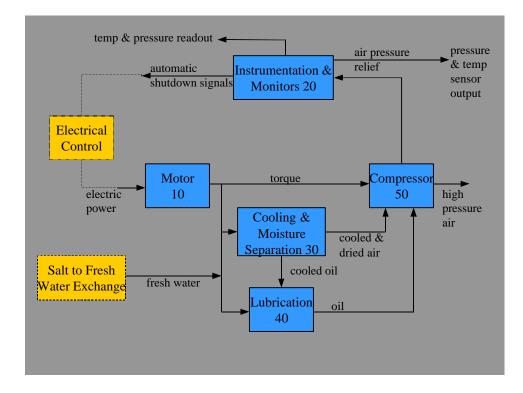

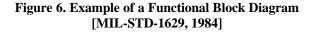

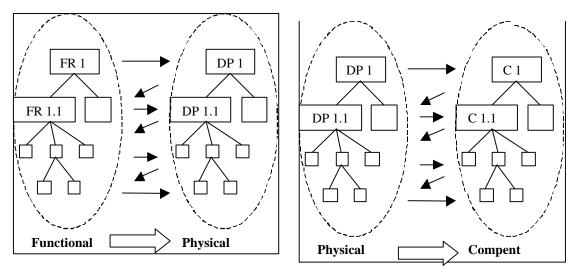

The term BIST is sometimes used interchangeably with BIT. However, BIST is usually associated with low level circuit card assembly tests. This level of testing is characterized by well-developed standards, technologies (IEEE 1149, boundary scan, and signature analysis) and tools. [Drees, 2001] The middle level of BIT testing, the Instrument Level, refers to programmable instrumentation in supports systems or LRUs in military systems. The highest level, System Level BIT, tests the entire system. A key requirement of this level of test that is not levied on the other BIT levels is fault isolation, the ability for a test to diagnose the failing lower level LRUs. Figure 1 shows an example of the different levels of BIT testing.

Figure 1: BIT has Specific Meanings for Specific Assembly Levels

BIT requirements represent the minimum essential levels of performance desired by the customer. BIT requirements can include the following types of requirements [MIL-STD-2165, 1989]:

- The proportion of failures to be detected automatically (versus manual troubleshooting such as swapping large items, manual probing, etc)

- Maximum acceptable failure latency

- Frequency at which periodic BIT will run

- Maximum BIT false alarm rate

- Fault isolation by BIT to a subsystem or lower level part

- Maximum fault isolation time

#### 2.3 Common BIT Requirement Verification Methods

A number of approaches to verifying BIT requirements are used on military and commercial programs. Each approach is valid but has strengths and weaknesses in different areas. [Devlin, 1999] The verification method is not always chosen for appropriateness – at times it is directed by the customer, engrained in the company process or the only available option. Industry standards have been created for initiating BIT and for formats of error and status responses. However, no industry standard has been published for BIT fault coverage or isolation, the two most common BIT requirements. [Drees, 2001] Table 1 lists several common verification methods with a description and an explanation of the strengths and weaknesses of the method.

| Verification Method      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pros/Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component Based Methods  | System design is analyzed and a<br>list of all testable components<br>generated. BIT tests are created<br>to test all components.<br>Components are removed from<br>the test list if they become too<br>time consuming or costly to test.<br>Fault detection percentages are<br>based on the number of<br>components tested versus the<br>number of testable components.                                                                                            | Pros: All testable hardware<br>components are considered for<br>BIT. There is a small chance of<br>failures occurring undetected.<br><u>Cons</u> :<br>Costly approach due to the<br>number of BIT tests required.<br>BIT circuitry may have to be<br>added to test some components.<br>Many BIT tests are redundant.<br>Fault isolation becomes difficult.<br>False alarm rates can be high.<br>True component based analysis<br>is difficult because it requires in<br>depth system knowledge.                |

| Statistical Methods      | Statistical reliability data is<br>gathered on the system<br>components. BIT tests are<br>designed on probability of failure<br>based on the failure rate of the<br>component and where it is used.<br>If a component has a high<br>probability of failure, a BIT test<br>is created for it. Components<br>with low failure rates are not<br>tested. Fault detection<br>percentages are based on the<br>number of high probability of<br>failure components tested. | DescriptionPros:Redundant tests areeliminated because everycomponent is not tested.Costeffective because BITdevelopment time and dollars arefocused on problem areas.Cons:System functionality isnot considered.Importantfunctionality can be overlookedbecause it is very reliable, but theassociated failure is missioncritical.High-risk componentsthat can cause loss offunctionality (mission critical) orsafety critical items may not beincluded in the BIT tests.Faultdetection percentages may below. |

| Functional Based Methods | The functionality of the system<br>or subsystem is analyzed and a<br>BIT test is created for each<br>functional task. Complex<br>functions may require several<br>BIT tests. Fault detection<br>percentages are based on the<br>functional tasks tested.                                                                                                                                                                                                            | <u>Pros</u> : All critical components are<br>tested as part of their associated<br>function. Mission and safety<br>critical components are included<br>as part of the functionality.<br><u>Cons</u> : All combinations of<br>components that can lead to loss<br>of functionality may not be<br>considered. In this case, fault<br>detection may not cover all<br>functionality. Low reliability<br>components (that are not critical)<br>may not be tested.                                                   |

#### Table 1. Common BIT Requirement Verification Methods

| Verification Method       | Description                                                                                                                                                                                                                                                                                                                                                                                                                         | Pros/Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Level Test Methods | BIT tests are created only to fill<br>gaps that cannot be tested at a<br>system level. All functionality<br>that can be tested at a system<br>level is excluded from BIT. 'As<br>good BIT is, in our experience, it<br>should only be used as a building<br>block when used in a system-<br>level test.' [Drees, 2001] Fault<br>detection percentages are based<br>on the number of functional tasks<br>not tested at system level. | <u>Pros</u> : BIT development is kept at<br>a minimum. Additional BIT<br>circuitry is rarely needed. Fault<br>detection percentages cover only<br>a small part of the system.<br><u>Cons</u> : This method assumes<br>system levels tests will be<br>performed often and are readily<br>available. If the system level test<br>is not performed often enough,<br>fault detection drops<br>dramatically. An incomplete<br>system analysis may leave some<br>functionality not tested. |

| Customer Defined Methods  | Customer defines a set of BIT<br>tests to be executed on a<br>program. Percent detection is<br>based on the number of tests<br>performed on the customer-<br>defined list.                                                                                                                                                                                                                                                          | <u>Pros</u> : The fault detection rate is<br>easily verified. Responsibility to<br>verify BIT requirements can fall<br>on the customer and not the<br>contractor.<br><u>Cons</u> : Only as good as the data<br>provided by the customer. Some<br>components and functionality<br>may not be included. A false<br>alarm rate requirement can be<br>difficult to meet if the customer<br>defined BIT tests do not cover<br>the system adequately.                                      |

#### 2.3.1 Who Performs BIT Requirements Verification?

BIT requirement verification is a task that can be performed by several different groups. Systems Engineers or Specialty Engineering (Reliability, Maintainability, etc) engineers on the program sometimes perform the verification. Some companies have separate functional groups specializing in requirements verification that perform the analysis and requirements verification. Others may use outside contractors or consultants that are hired to perform a one-time BIT analysis and verification. In some cases, the customer may perform the BIT requirements verification.

<u>Program Engineers</u> – Program engineers provide continuous analysis as program time and dollars permit. Engineers have the most intimate knowledge of the system design. BIT tests tend to be thorough and well documented, but there is a chance of the final verification results and analysis being skewed to show BIT requirements are met. Engineers have a vested interest in the program

succeeding and may provide the design information in such a way to ensure the verification goes favorably.

<u>Functional Group</u> – Tends to be one of the more accurate analyses because, since it is an internal (to the company) group, information is more readily available. Program engineers can be interviewed and actual hardware examined. Questionable results can be reevaluated. Difficulty comes when trying to adjust the requirements definitions from the customer point of view to the traditional requirement definitions of the group.

<u>Consultants</u> – Consultants review the design and suggest BIT tests. Their analysis shows how the list of BIT tests satisfy the BIT requirements. The analysis is not biased and is usually very thorough based on the information the consultants gather. This requires much coordination from program engineers to provide information to the consults. However, the assumption has to be made that all the BIT test are implemented and that the system design does not change. Consultants tend to be a one-time effort so programs with changing designs are not benefited from the method of verification.

<u>Customer</u> – The benefit of the customer performing the verification is that the results, if satisfactory, are automatically accepted by the customer. Accurate results are hard to come by because the system may not be as well known by the customer as by the program engineers. However, the analysis can be revisited because the customer has constant access to the program.

#### 2.3.2 BIT Requirements Verification in the System Development Process

BIT Requirements verification can start in any phase of the system development process. The final verification cannot take place until the system is fully developed and the design is stable. However, the earlier the BIT requirements verification begins, the easier it is to obtain results.

The System Development Cycle consists of four main phases: Design, Development, Test and Production. If BIT analysis and requirement verification efforts begin in the design stage, the appropriate BIT circuitry can be included in the design, design information can be collected for the required analysis and information intentionally stored to help with the verification process. One disadvantage to start BIT requirements verification in this phase is that there will be many changes to the design and some effort will be wasted will the designs change. In the development phase, actual design data is captured and BIT tests are being implemented. Reliability tools, computer programs that take reliability data and compute testability numbers, can be used in this phase to capture design data and automatically produce verification proof. The reliability tools are extremely helpful, but care must be taken to ensure all system components are considered or realize the output of the reliability tools is not a complete assessment. There is a smaller risk of design change in this phase.

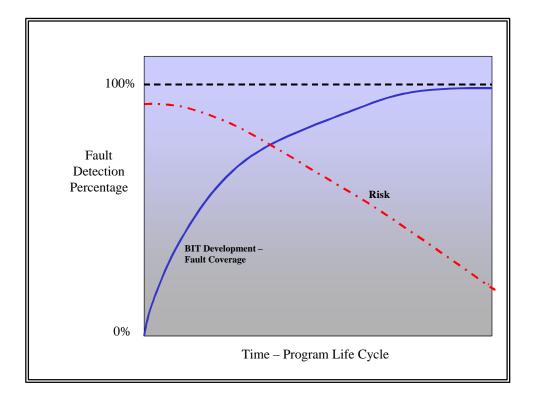

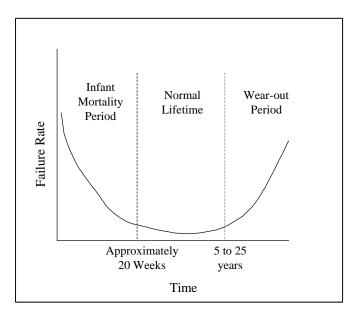

The test phase marks an essentially complete design. Only minor changes should take place in this phase. All possible failures may not be detectable by BIT circuitry and it may not be cost effective to implement logic to detect them. As the program develops, more BIT tests are developed and the failure detection percentage increases. Likewise, the risk to the program decreases. Eventually a point is reached where the risk is less of a cost to the program than implementing more fault detection measures. Figure 2 shows fault coverage takes a logarithmic curve with respect to time.

**Figure 2: Fault Coverage**

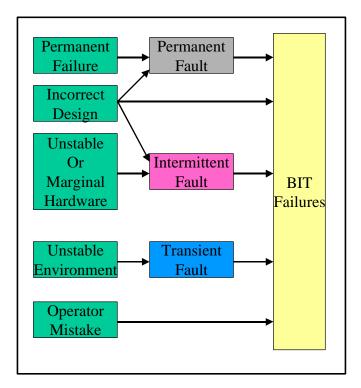

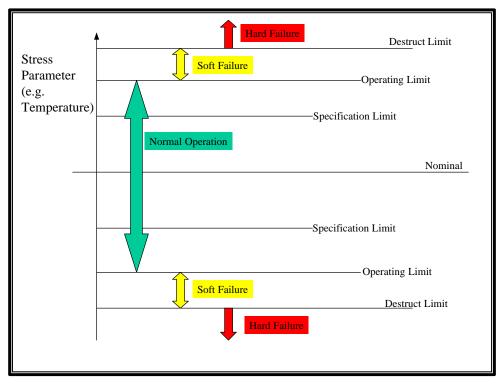

All sources of BIT failures can be identified the testing phase. Not all BIT problems are a result of the system design. BIT tests can fail due to certain environments and hardware or even operator mistakes. See Figure 3 for an example of the many different causes of BIT failures. The testing performed in this phase identifies many of such issues. The BIT requirements verification should be complete by the end of this phase.

**Figure 3: Sources of BIT Failures**

In the production phase, the design has been finalized and all BIT requirements should have been verified. Occasionally minor changes or enhancements may take place during production and the BIT requirements verification may need to be revisited. Lack of adequate documentation of the BIT verification can make this task difficult.

#### 2.4 Difficulty of Verifying Requirements on Existing Systems

Despite the apparent sophistication of BIT, and the fact the BIT requirements have been verified, there has been some concern that the requirement for BIT and the actual capabilities and limitations of the BIT have not been properly identified. For example, airline experience with

modern avionics systems has indicated spurious fault detection is unacceptably high. The system BIT requirements have not actually been met.

For instance, the Airbus A320, Lufthansa, had a daily average of 2000 BIT failures logged. 70 of these corresponded to failures reported by pilots, while another 70 faults not detected by BIT were reported by pilots. Of the 17 line replaceable units (LRUs) replaced every day, typically only 2 were found to have faults that corresponded with the report. Thus even for commonly observed problems, fault detection is not complete and false alarms occur. [Pecht, 2001]

The Airbus A320 is an existing design in which new functionality and capabilities have been added through the years. As this occurs, the supporting BIT was developed and verified. Why is there such a discrepancy in fault detection and reporting? It is because of the difficulty in verifying BIT requirements on an existing system.

#### 2.4.1 Adverse Factors in Existing Designs

With a new design or a development project, information can be gathered for the BIT analysis and verification as the design proceeds. BIT is planned for and is a consideration in the design. BIT circuitry is added and the design is evaluated so the engineers know what is necessary to meet BIT requirements.

This is not the case in a situation where BIT requirements are being verified on an existing system. BIT may have been planned in the development of the program or it may have been added later. Several common problems and concerns when verifying BIT requirements are listed below:

- Incomplete or incorrect BIT analysis when starting with a baseline. This can

occur when assuming the original or previous BIT analysis was correct or

complete. In this case the existing numbers are used and only the new BIT

tests and functionality are examined. Sections can be missed in the older

analysis or performed incorrectly, causing the result to be incorrect.

- Incompatible data types when starting with a baseline. Reusing older BIT analysis data can be misleading if the data format is not understood. Percentages and rates should be clearly defined to ensure the definitions are

compatible with the way they are being used in the new analysis. Lack of attention to this detail can lead to incorrect results.

- Lack of data to perform analysis. Older programs may not have documented all program design, or it may have been lost, or what is in the current documentation may be out of date.

- True state of current system may not be known. The history of the program may not be known decisions or changes may not be documented. The true configuration of the system could require reverse engineering to determine the current state.

- The task is overwhelming and not cost efficient. The program budget may not allow for the time necessary to reanalyze an entire system or a large system that has had multiple changes.

#### 2.5 Description of HTI System

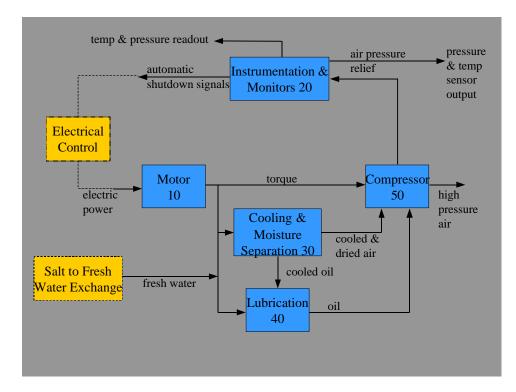

As an example and the test system for the BIT Analysis process, this project will include a BIT analysis on the HTI Second Generation Forward Looking Infrared (FLIR) sensor. The HTI FLIR is a scanning infrared receiver that collects radiation in the 8-12 micron spectral region across two different 2-D fields of view using a second generation IR focal plane array. The SGFLIR is composed of several modules, each having pre-defined interfaces and physical connections that allow it to function as a stand-alone unit or to be integrated into a host platform. It is designed to be versatile – with most of its image processing implemented in software and firmware to improve flexibility and decrease the complexity of the hardware. [MIL-PRF-A3207380, 1997]

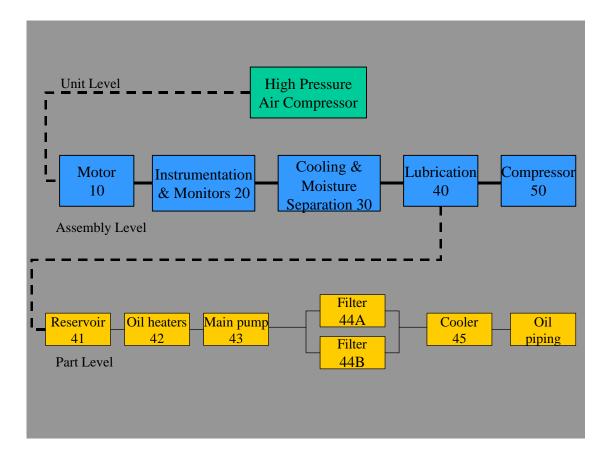

The HTI FLIR, commonly called a B-KIT, is packaged so that it can be housed on multiple platforms. Thus, there is some functionality related to the particular host using it and this functionality must be tested with BIT. Figure 4 shows the components that comprise a B-KIT. The number of circuit card assemblies (CCAs) gives an indication to the complexity of BIT required to test all functionality.

Figure 4: HTI B-Kit Components [Raytheon4, 2002]

#### 2.6 BIT Requirements on HTI

The HTI FLIR is an existing design that has BIT tests implemented and specific requirements for failure detection percentages and false alarm rates. The BIT requirements are defined in the HTI Performance specification and are listed below: [MIL-PRF-A3207380, 1997]

- <u>1) BIT quantitative requirements</u>. For the purpose of the following subparagraphs, the term BIT includes IBIT, the interactive BIT of the host platform, and operator detection/isolation of failures. Operator detected/isolated failures will be such that they are obvious and require no judgment to determine that the observed artifact or condition is a failure.

- 2) Detection by BIT. The B-Kit shall be designed such that at least 90 percent of the B-Kit failures can be detected using BIT.

- 3) Isolation by BIT. BIT shall isolate to the failed LRU for at least 85 percent of the B-Kit's failures.

- <u>4) BIT false alarm rate</u>. BIT false alarms shall not exceed a 2 percent rate when no failure is present.

- 5) Power-up BIT (PBIT). The B-Kit shall provide the capability for PBIT tests that are performed on the B-Kit at power up. At a minimum, PBIT shall test and determine the status of all applicable power conditioning devices, the basic processing capability, and the status of all major internal and external communications ports of the B-Kit. PBIT shall not be abortable. At the

completion of PBIT the B-Kit shall enter the operate mode regardless of BIT status.

- 6) Start-up BIT (SBIT). The B-Kit shall provide the capacity for BIT prior to the complete cooldown of the detector/dewar assembly. SBIT shall consist of all initial tests not conducted at power-up. SBIT shall be abortable. SBIT, when coupled with PBIT, CBIT, and the interactive BIT of the host platform, shall be capable of detecting at least 90 percent of the NV-80 B-Kit's mission critical failures. SBIT shall not be performed if the focal plane array (FPA) is already at operating temperature when power is applied to the B-Kit.

- 7) Continuous BIT (CBIT). The B-Kit shall provide the capability for CBIT performed while the B-Kit is operating to detect mission affecting failures. This CBIT, when coupled with the interactive BIT of the host platform, shall detect at least 85 percent of mission critical failures in the B-Kit. CBIT shall detect at least 90 percent of the mission critical failures in the B-Kit when coupled with the interactive BIT of the host platform and operator detection. These tests shall not degrade the B-Kit imagery or symbology performance.

- 8) Operator initiated BIT (IBIT). The B-Kit shall provide the capability for operator IBIT tests. This IBIT shall be completed within 35 seconds. The B-Kit is not required to be imaging while these tests are being performed. Operator IBIT shall be abortable via the BIT interrupt.

- <u>9) Fault isolation using BIT</u>. The B-Kit shall make provisions to allow external control of those BIT tests where the state of a given signal must be held for external observation per the B-Kit ICD.

Table 2 shows the BIT requirements and the predicted performance for older versions of the B-Kit. The entries in the table are a result of the original B-KIT BIT analysis and requirements verification. The performance is evaluated with two different B-KIT software versions (v3.01 and v4.0) and two different hardware configurations (Engineering Manufacturing and Development (EMD) and Low Rate Initial Production (LRIP)). The false alarm rate requirement is not addressed in the analysis and is not included in this table.

|                                           | Detection % (+/- 5%)                                        |                                                                              |                                                                                 | Fault<br>Isolation %<br>(+/- 5%)                      |                                                    |

|-------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|

|                                           | CBIT + Host<br>Platform<br>Mission<br>Critical<br>Detection | CBIT +<br>Operator +<br>Host<br>Platform<br>Mission<br>Critical<br>Detection | PBIT + SBIT<br>+ CBIT +<br>Host<br>Platform<br>Mission<br>Critical<br>Detection | IBIT +<br>Operator +<br>Host<br>Platform<br>Detection | IBIT +<br>Operator +<br>Host Platform<br>Isolation |

| Current B-KIT Performance<br>Spec         | 85%                                                         | 90%                                                                          | 90%                                                                             | 90%                                                   | 85%                                                |

| Version 3.01 EMD Predicted<br>Performance | 86%                                                         | 90.1%                                                                        | 91.9%                                                                           | 90.8%                                                 | 85.9%                                              |

| Version 4.0 LRIP Predicted<br>Performance | 86%                                                         | 90.1%                                                                        | 91.9%                                                                           | 90.8%                                                 | 89.6%                                              |

Table 2. HTI BIT Detection and Isolation Requirements and Predicted Performance

[Raytheon1, 1997]

#### 2.7 Description of the Need for BIT Analysis on HTI

An analysis was performed in 1997, early in the HTI program, on a previous design (the EMD hardware) and predictions made for the newer LRIP hardware. Pertinent data from the original analysis is contained in Appendix II.

#### 2.7.1 Original Analysis Results

The analysis emphasized a reliability-based approach to determine the detection and isolation performance of the B-Kit BIT functions. The study examined individual components or functional groups of components and determined, via analysis, if the BIT software would detect a failure in the component. If it could detect the failure then the failure rate for that component, or a percentage of the failure rate, was added to the BIT software detection "bucket". The same process was used for determining Operator and Host Platform detection percentages.

After all components were examined a total was struck and detection percentages computed for each detection category. These in turn were combined to arrive at percentages for each combination in Table 2. Failures that could be detected by multiple categories were only counted once when computing the roll ups to avoid duplication.

The above purely analytical approach was augmented by referring to experience derived from failure injection, actual use of the system, and experience on other programs. Isolation predictions for the BIT software were determined by applying the software Version 3.01 fault isolation algorithm to the predicted BIT failures. Rules were also established for Operator and Host Vehicle Isolation and these rules were applied to the predicted detection results. [Raytheon1, 1997]

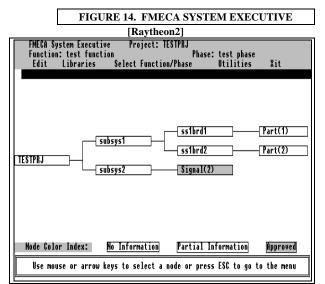

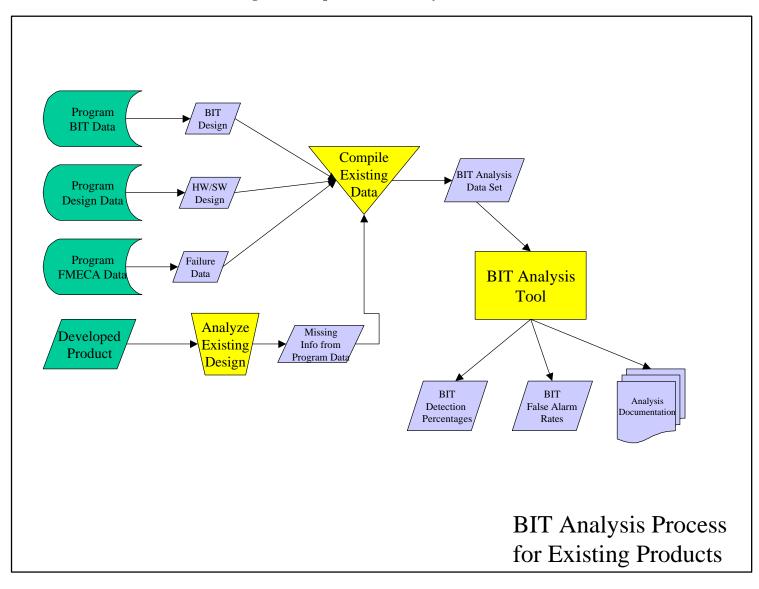

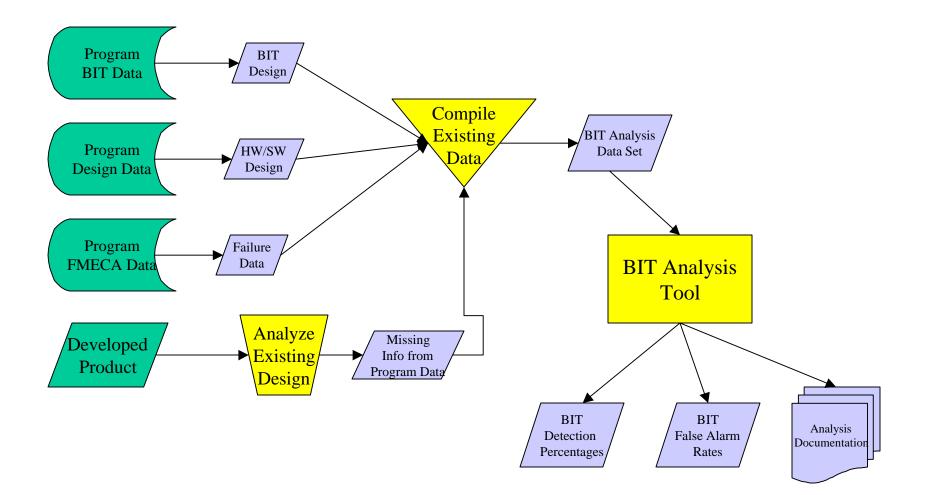

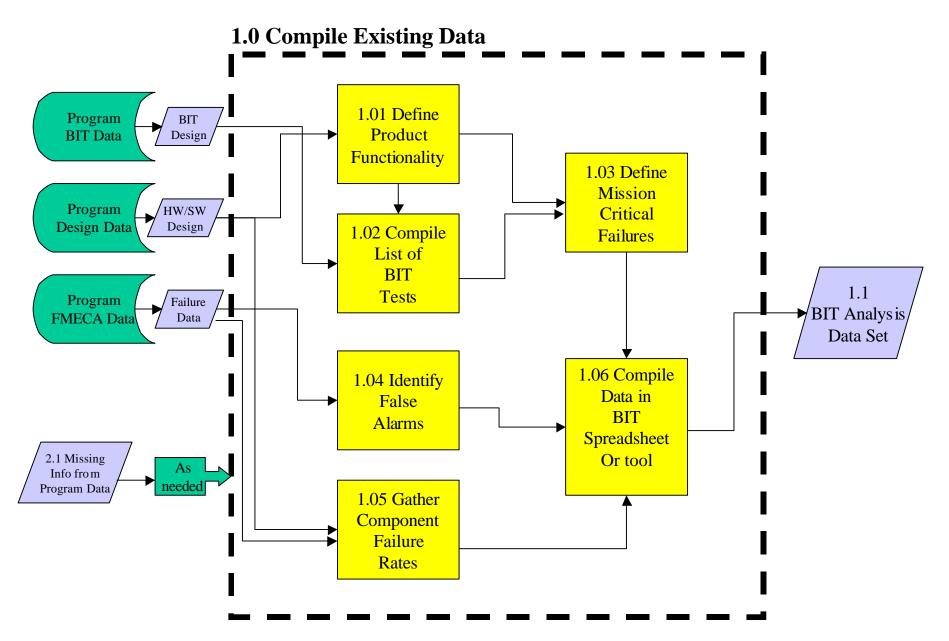

#### 2.7.2 Modification of Original Data